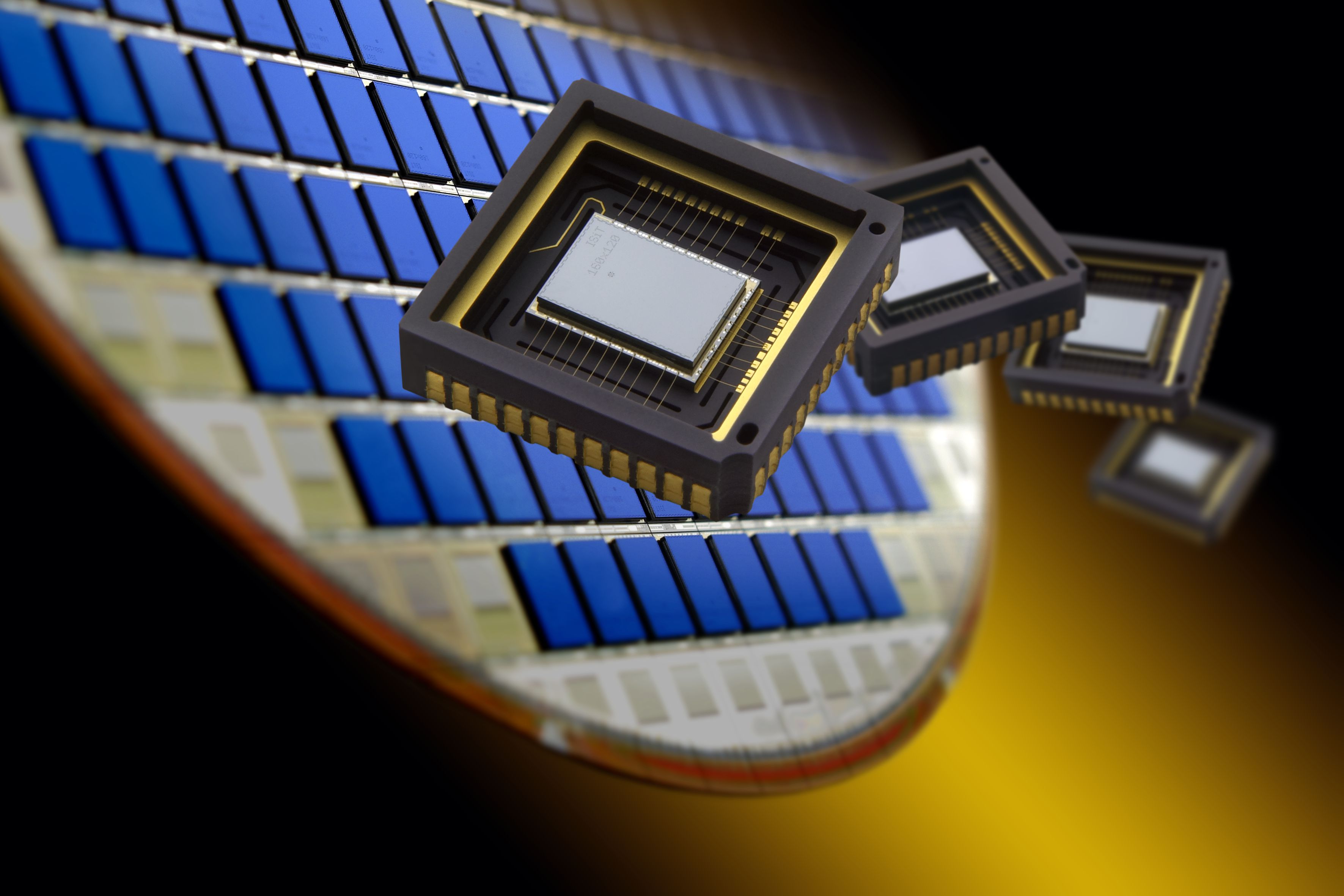

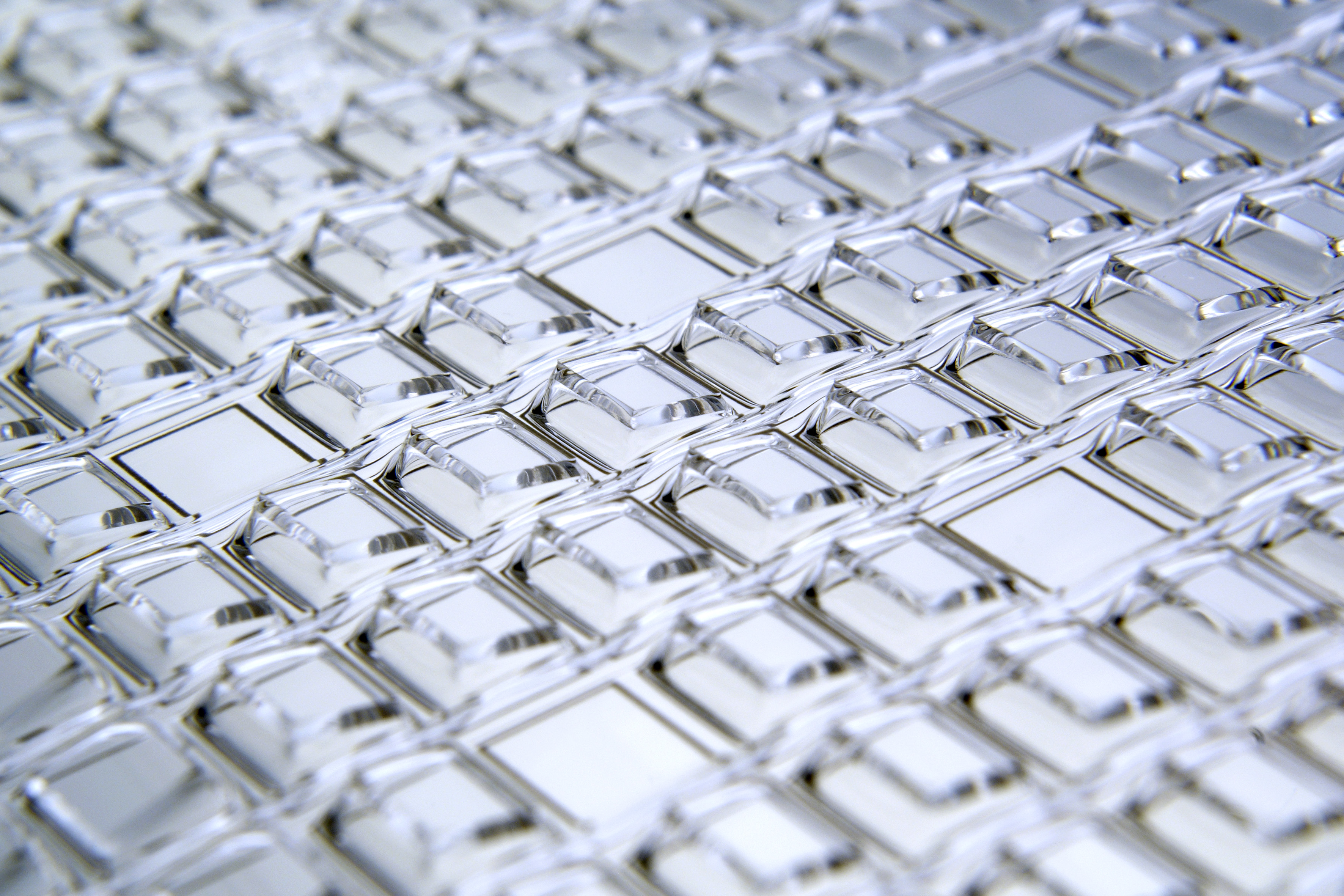

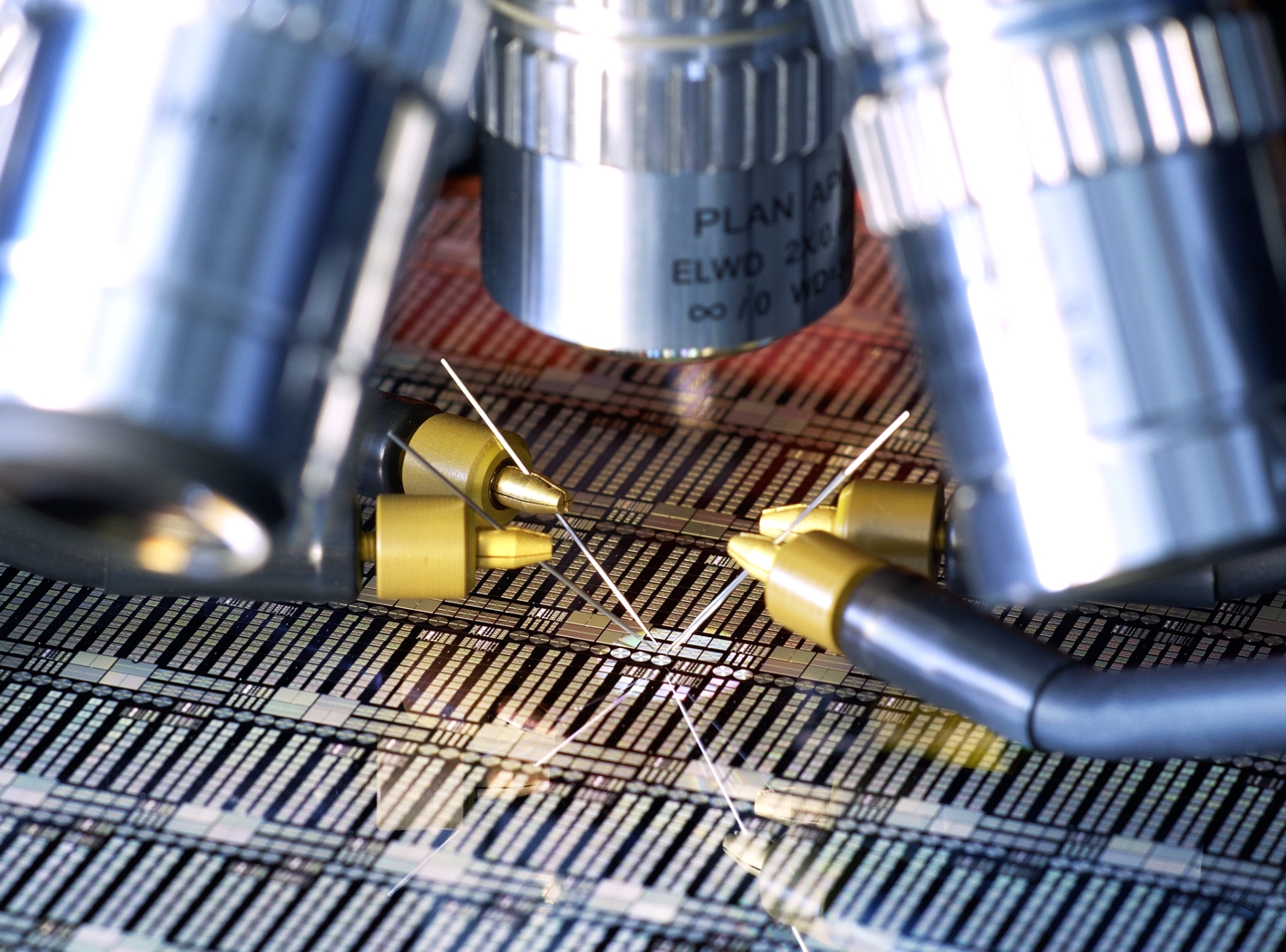

Die Gehäusung von Mikrobauteilen auf Waferebene nutzt die Präzision der Halbleiter- und Mikrosystemtechnologien zur Realisierung robuster und äußerst kompakter Aufbauten. Der spezielle Fokus liegt dabei im ISIT auf der hermetischen (Vakuum) Verkappung von Mikrosensoren und Aktuatoren sowie mikrooptischen Komponenten mittels verschiedener Fügetechnologien wie Glaslote oder Metalle (IR-Imager Wafer mit IR-Fenstern aus Si). Für mikrooptische Komponenten können Gehäuse mit optisch transparenten Fensterflächen für den sichtbaren Bereich bis zu fernem Infrarot hergestellt werden. Das Wafer Level Packaging eignet sich auch für die Post-CMOS Prozessierung von kundenseitig beigestellten Wafern. Einsatzgebiete der Technologieplattform sind unter anderem IR-Sensoren und IR-Imager, Inertialsensoren, Magnetfeldsensoren, Harvestern und MOEMS-Bauteile. Das ISIT verfügt über eine moderne 200 mm Entwicklungslinie für Mikrosysteme, Glas-Silizium Substratwafer mit hermetischen Vias und funktionalisierte Kappenwafer. Die industriell ausgerichtete Entwicklungsumgebung und Chargensteuerung ermöglicht einen einfachen Technologietransfer für die Volumenfertigung. Zusammen mit der im Haus vorhandenen Expertise zur Messtechnik, Aufbau- und Verbindungstechnik, Qualitätsbewertung und beschleunigten Alterung können vorqualifizierte Bauteile und Module auch in 0-Serien realisiert werden.

Fraunhofer-Institut für Siliziumtechnologie

Fraunhofer-Institut für Siliziumtechnologie