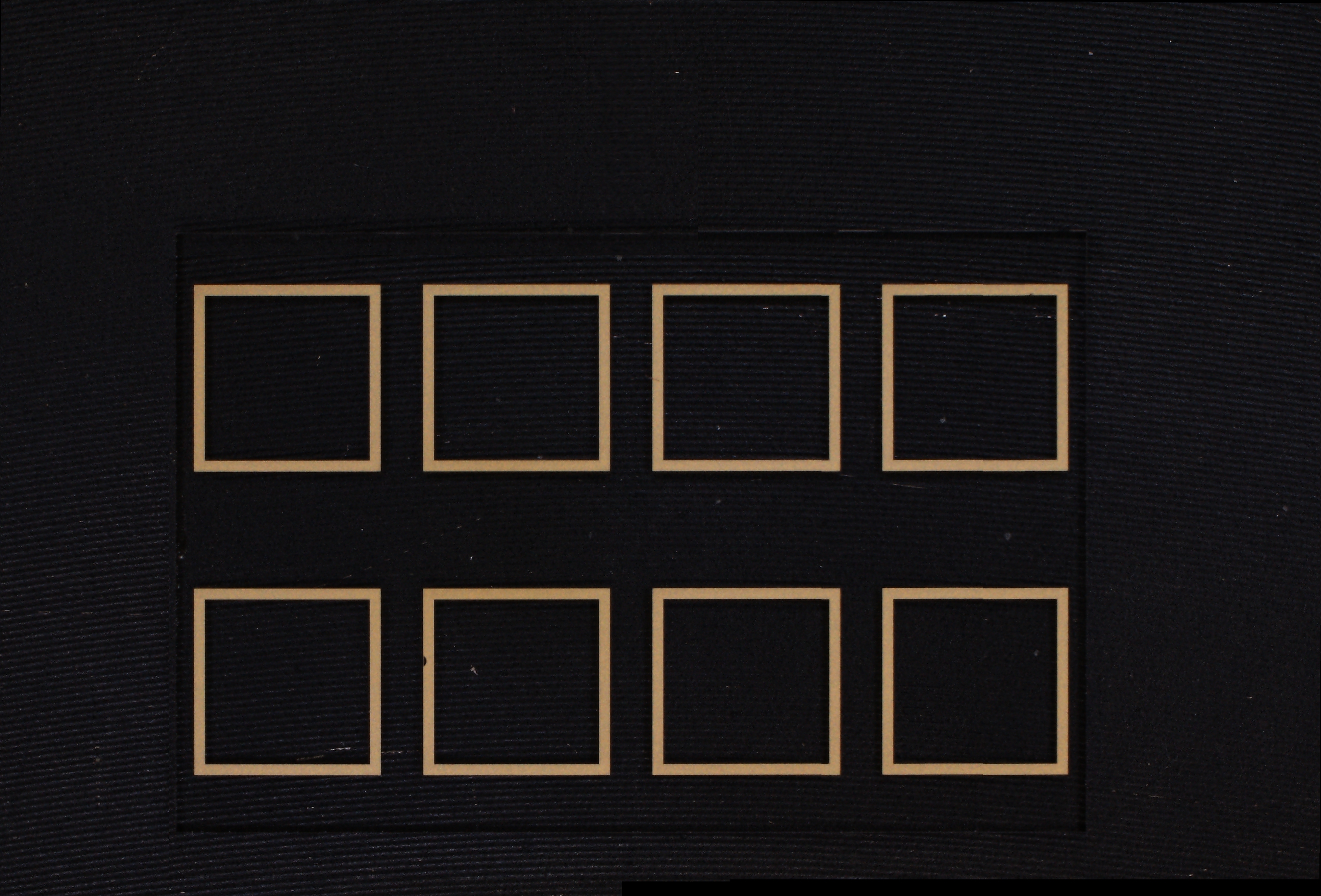

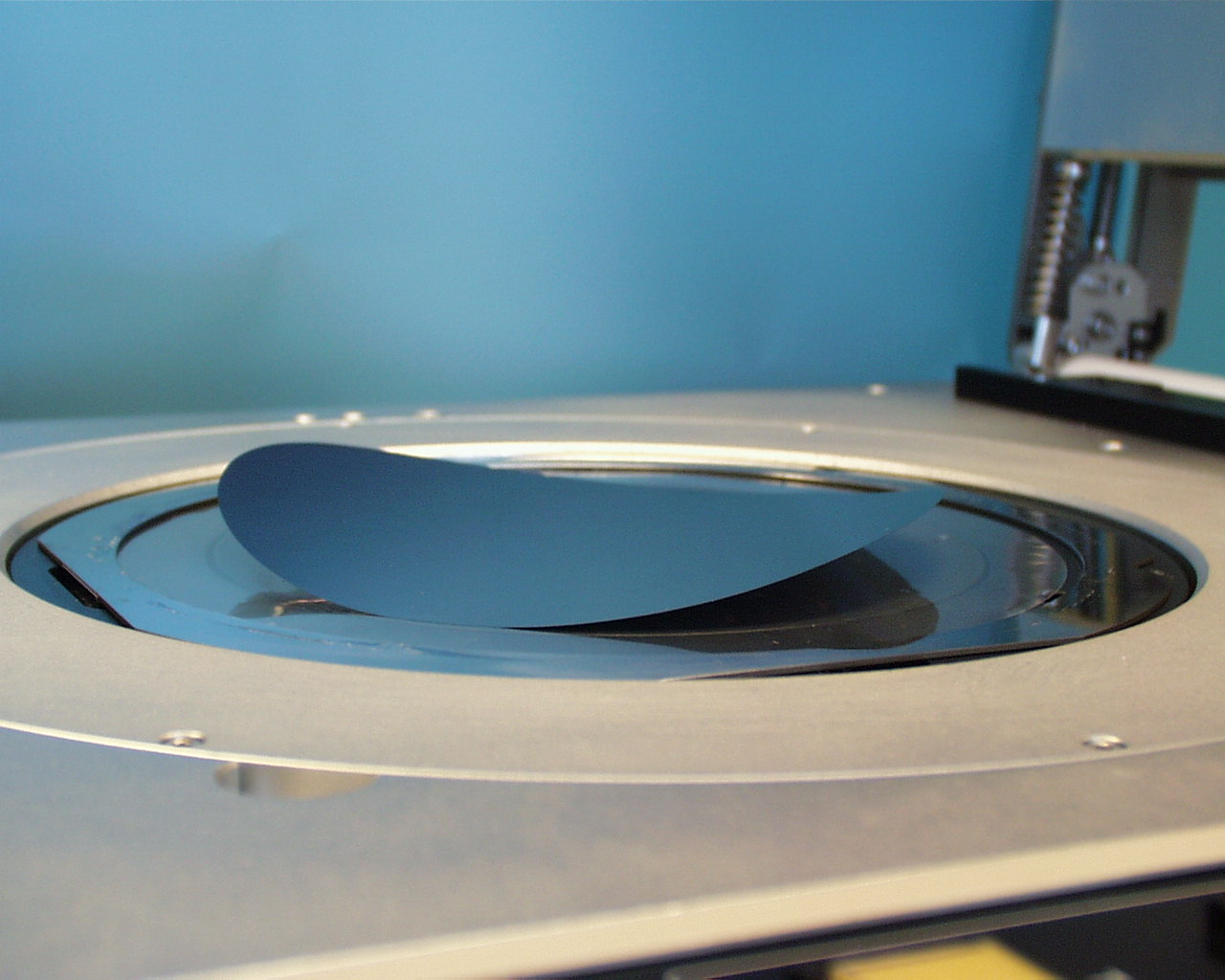

Testwafer aus Silizium werden auf denselben Anlagen hergestellt wie CMOS oder MEMS Produkte. Sie haben daher sehr ähnliche Eigenschaften in Bezug auf mechanische Eigenschaften, Oberflächenbeschaffenheit und Kontaktmetallisierung. Ihre Herstellung ist jedoch wesentlich günstiger, da im Vergleich zu einem funktionalen Produkt viele Prozessschritte entfallen können. Hinzu kommen Designfreiheiten, die das Testen stark vereinfachen können.

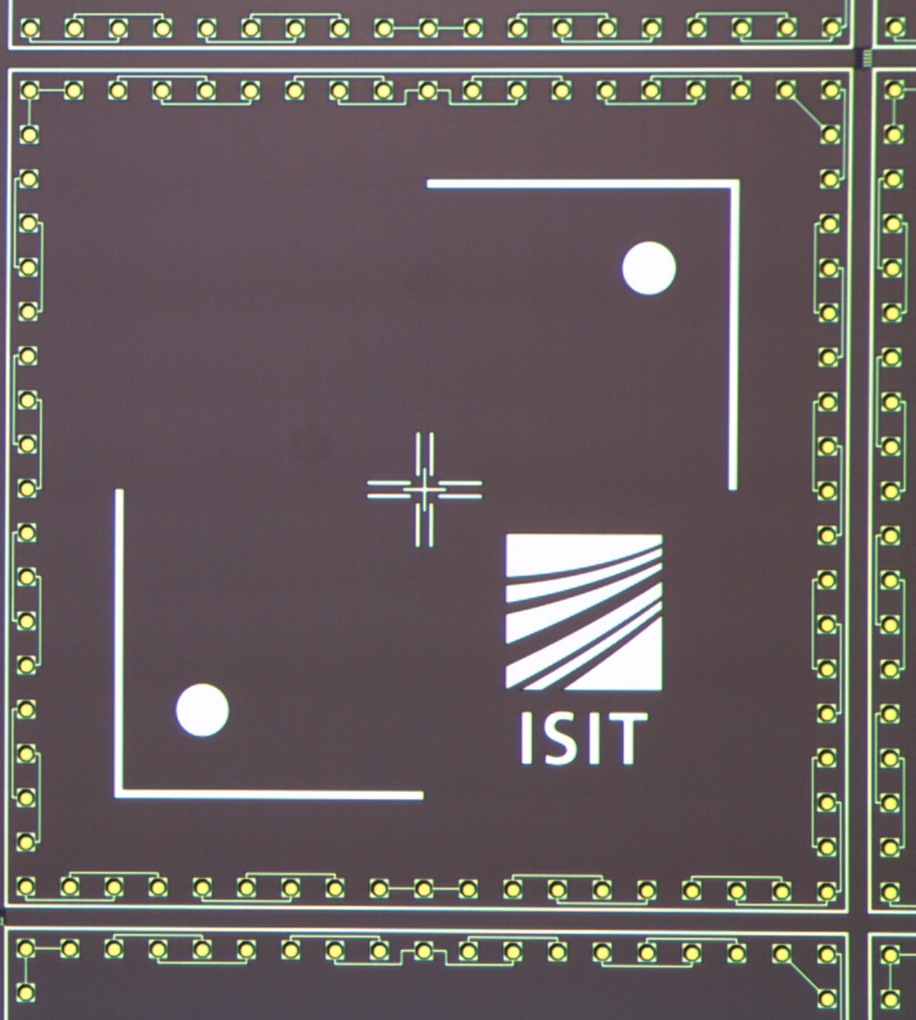

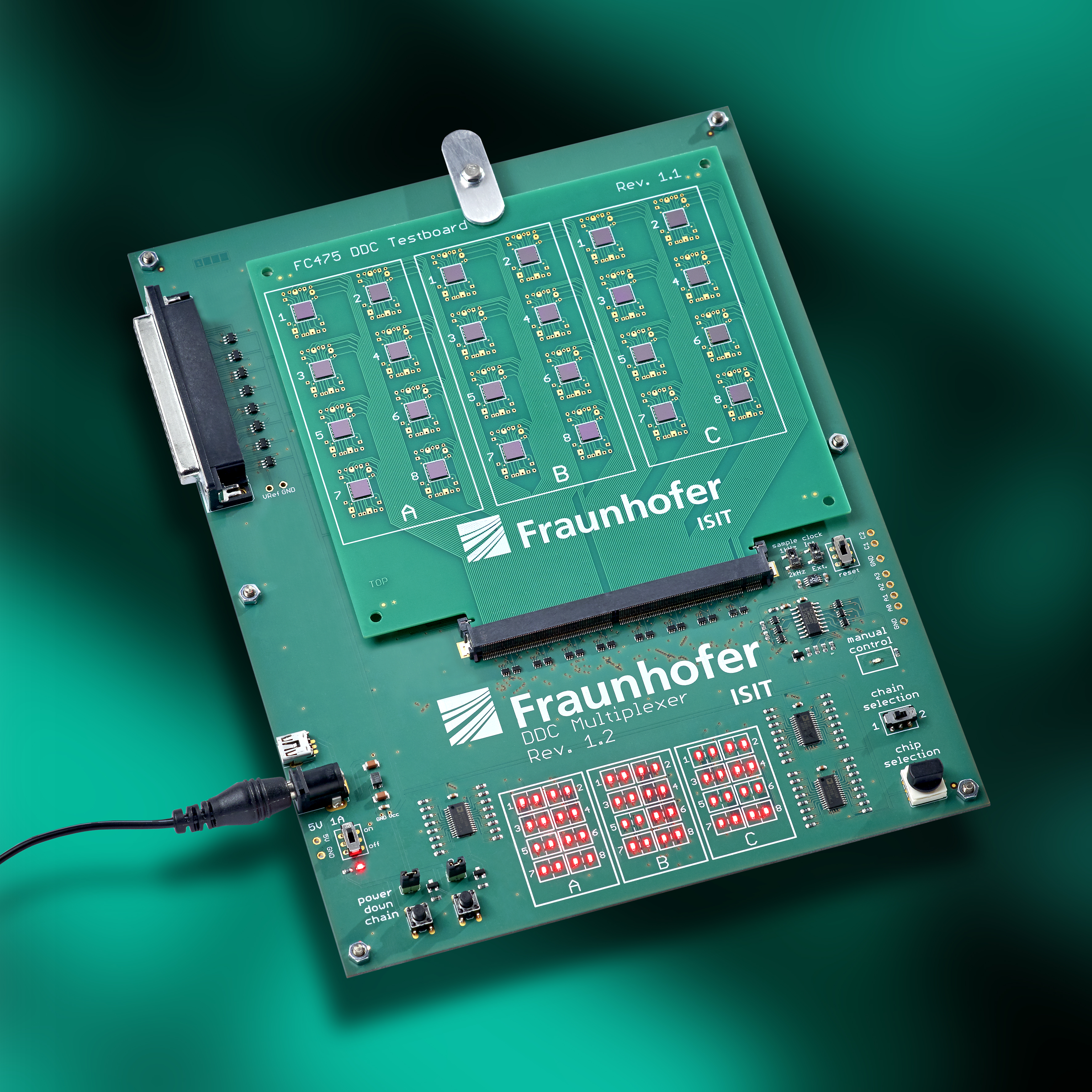

Fraunhofer-Institut für Siliziumtechnologie

Fraunhofer-Institut für Siliziumtechnologie