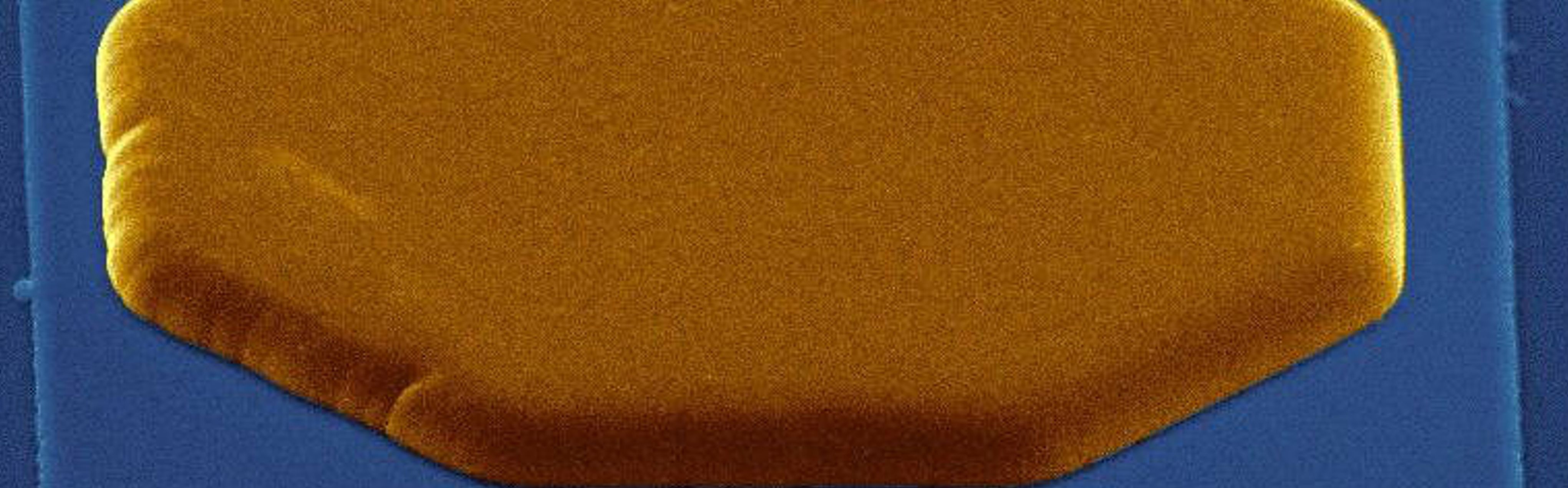

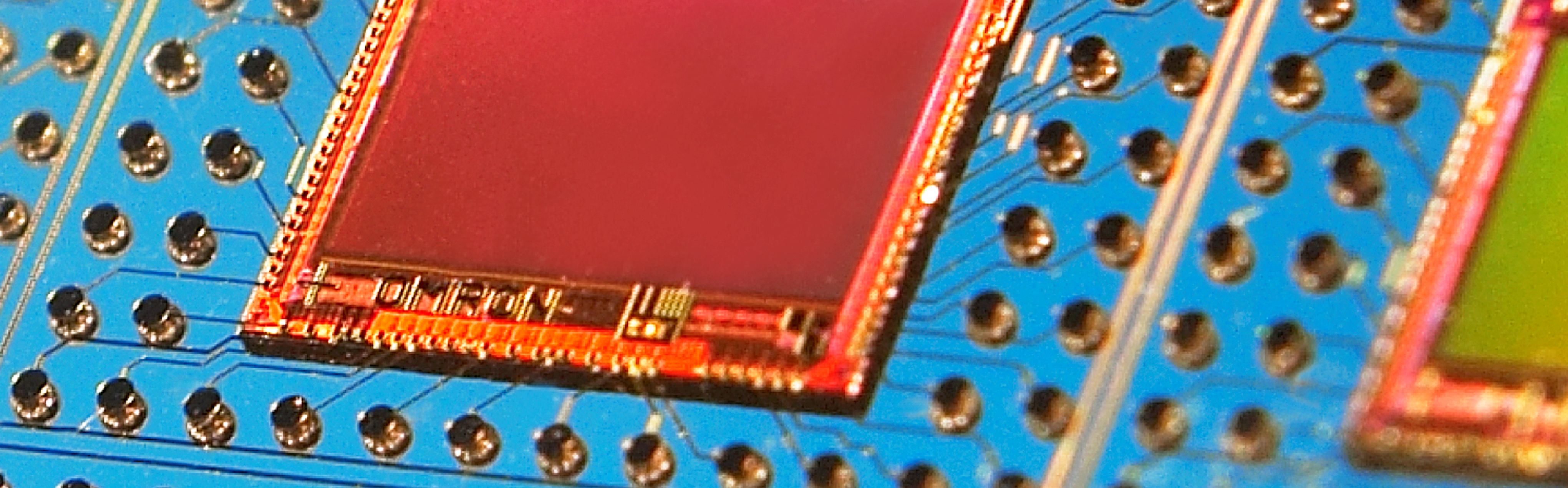

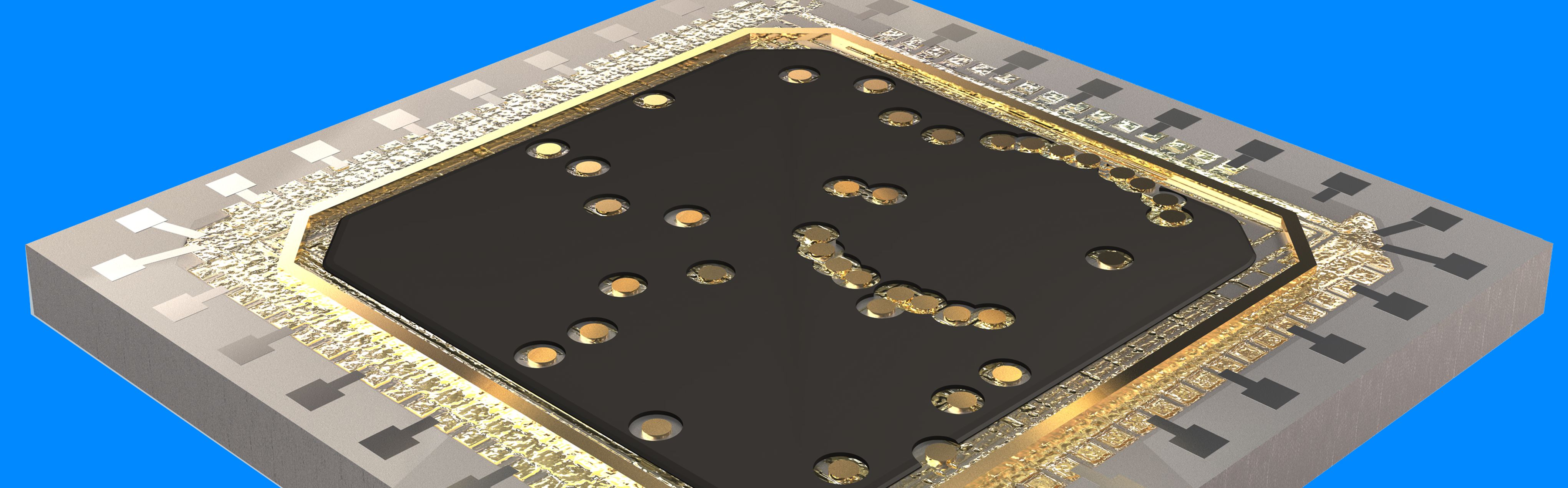

Der Einzug von Mikrobauteilen in mobile Elektronikgeräte zwingt zu extrem miniaturisierten Bauelementen mit Gehäusedicken deutlich unter 1 mm. Das ISIT ist spezialisiert auf die fortschrittliche Integration von Mikrobauteilen wie z.B. Inertialsensoren mit Auswerteschaltungen. Diese Aufbautechnik kann je nach Chipgeometrie und Komplexität auch auf Waferebene (WL-CSP) durchgeführt werden, wodurch besonders dünne Aufbauten realisiert werden können.

Das Institut hat hierzu einen modularen Werkzeugkasten an Schlüsseltechnologien entwickelt, der eine schnelle kundenspezifische Bauteilentwicklung erlaubt. Hierzu gehören:

- die symmetrische Waferdünnung von MEMS Bauelementen,

- spezielle Vereinzelungstechnologien zur Exposition der Bondpads,

- elektrische Durchführungen in Glas- und Siliziumwafern (TSV: Through-Silicon Via),

- Chip-Stapeltechnik mit Transfer-Klebefolien,

- Spacertechniken zur Chipmontage,

- 3D Drahtbonden und

- "Bumping und Balling", z.B. Lot-Bekugelung oder Stud-Bumping

Fraunhofer-Institut für Siliziumtechnologie

Fraunhofer-Institut für Siliziumtechnologie