Die folgenden Prozesse der klassischen Back-End Technologien sind am ISIT als Dienstleistungen insbesondere für MEMS-Bauteile verfügbar:

- Mechanisches Sägen (Dicing)

- Wafer-Dünnschleifen (Grinding)

- Aluminium- und Golddrahtbonden

- Die-Attach (manuell und vollautomatisch)

- Modulintegration als Chip-on-Board (COB), Multichip-Module (MCM)

- Dispensen von Vergussmassen (Glob-Top, Dam-and-Fill)

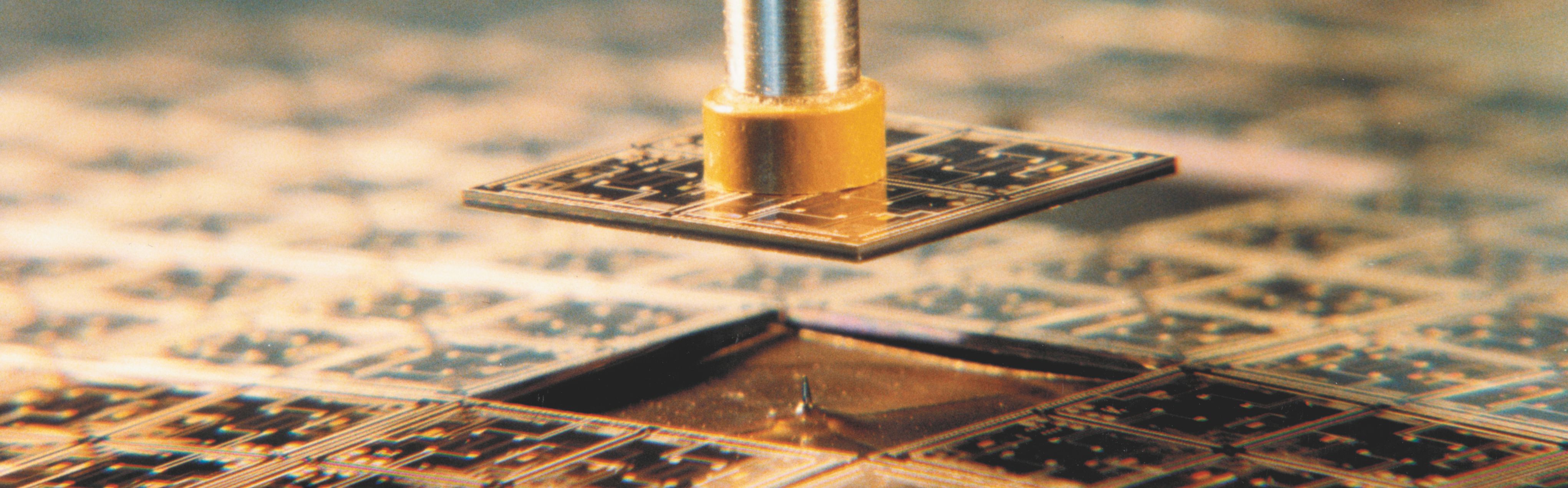

Als Erweiterung der Back-End Technologien auf Basis von Drahtbonden sind Flip-Chip und Chip-Size Packaging (CSP) vor allem in mobilen Anwendungen von großer Bedeutung. Das ISIT verfügt auch hier über Ausstattung und Technologie für alle grundlegenden Montagetechniken:

- Flip-Chip Bonden basierend auf Löten, Epoxy-Dip oder Stud-Bump Bonding (Ultraschallgestützt)

- Konditionierung von Wafern für Flip-Chip bzw. Chip-Scale Packages (CSP) durch Lot-Bekugeln bzw. Lotpastendruck

- Dispensen von Underfill-Klebstoffen

Das Fraunhofer Institut für Siliziumtechnologie bietet hierfür außerdem ein ausführliches Angebot an Testchips und Testsubstraten an.

Fraunhofer-Institut für Siliziumtechnologie

Fraunhofer-Institut für Siliziumtechnologie