Mikro-elektro-mechanische Systeme (MEMS) vereinen minimale Baugröße, niedrige Herstellungskosten und höchste Zuverlässigkeit und finden so vermehrt Anwendung in der Automobilindustrie. So werden MEMS Inertialsensoren für aktive und passive Sicherheitssysteme wie Fahrdynamikregelung aber auch Navigationssysteme eingesetzt, die auch in kostengünstigen Kfz-Baureihen zu finden sind. Doch auch im Consumerbereich finden Inertialsensoren eine breite Anwendung (Handy, Laptop, Spielekonsole). Um die Bauteildichte und Funktionalität weiter zu erhöhen, geht die Entwicklung von einachsigen Sensormodulen über mehrachsige Sensorsysteme hin zur kompletten inertialen Messeinheit (IMU), die die Gesamtbewegung eines Körpers in allen drei Raumachsen gleichzeitig erfasst.

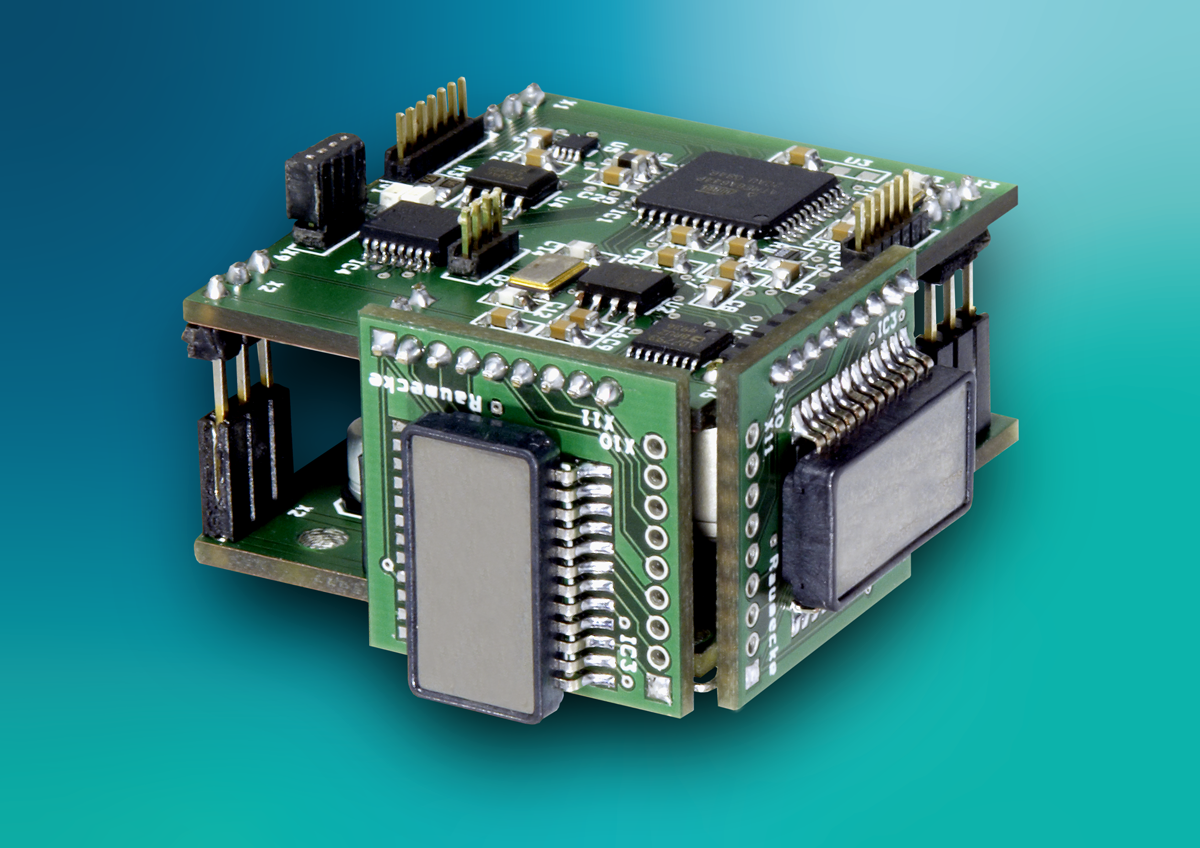

6-axis IMU device (inertial measurement unit, IMU)

Sensoren zur Messung von Drehraten, Beschleunigungen und Magnetfeldern haben mittlerweile in einer Vielzahl von Anwendungen Einzug in das tägliche Leben gehalten und machen die Nutzung vieler elektronischer Produkte unbemerkt wesentlich vielseitiger, einfacher und intelligenter. Zahlreiche neue Anwendungen im Bereich der Konsumgüterelektronik sowie Medizin- und Sicherheitstechnik sorgen für immer weiter steigende Marktanforderungen an intelligente Sensorsysteme, vor allem in Bezug auf Kosten, Baugröße, Qualität und Stromverbrauch. Solche Module bestehen aus einem Beschleunigungs-, Drehraten- und Magnetsensor mit jeweils drei Detektionsrichtungen und bilden damit eine 9D IMU. Damit ist eine präzise Positions- und Orientierungsbestimmung durch Auswertung des Erdmagnetfeldes und der Bewegungsmuster möglich.

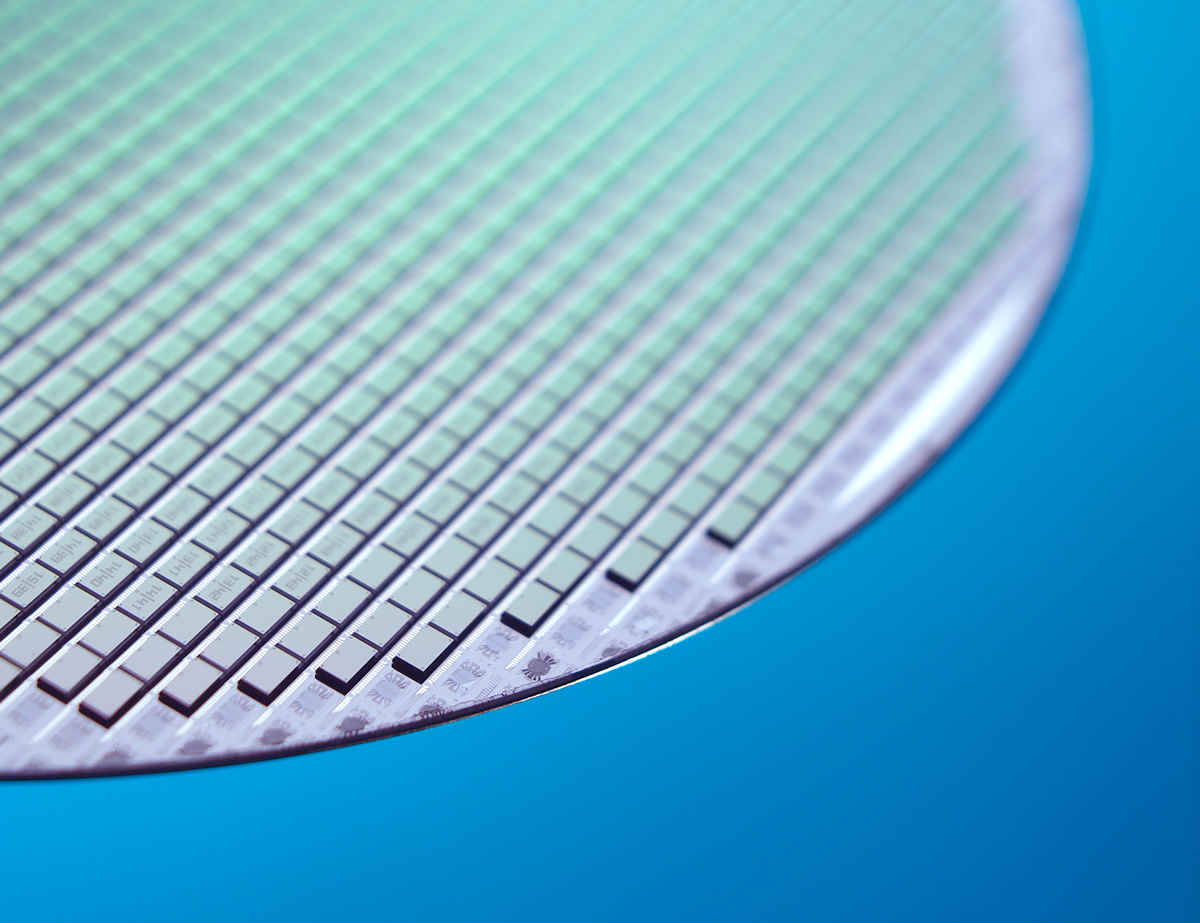

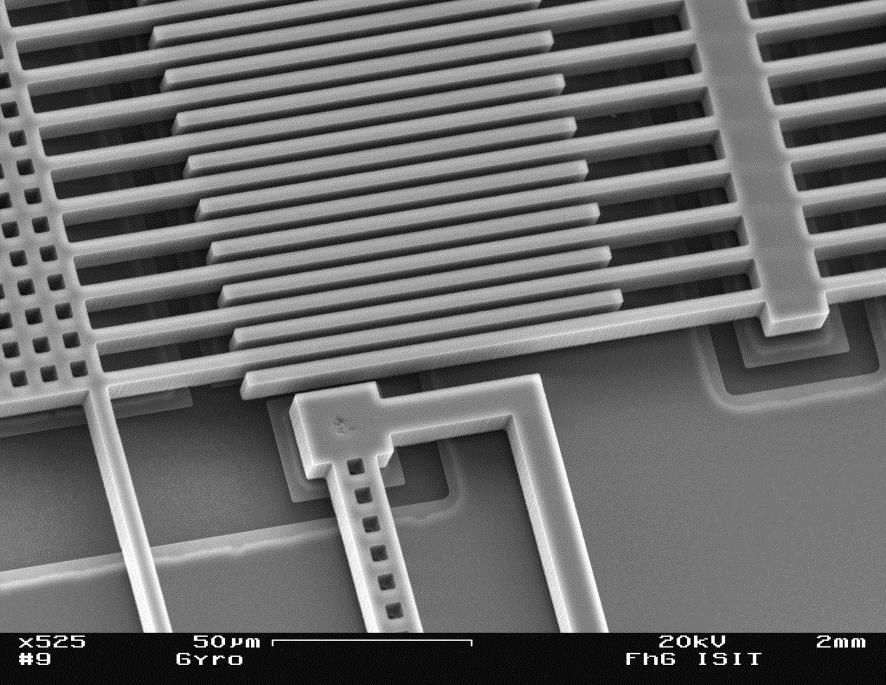

Während mittels Chip-Level-Integration 3-dimensionale Beschleunigungs- und Drehratensensoren schon in hohen Stückzahlen industriell gefertigt werden, stellt deren Kombination auf einem Chip aufgrund unterschiedlicher Anforderungen an die Betriebsumgebung weitaus größere Anforderungen an das Chip-Design und die entsprechende Fertigungstechnologie. Das ISIT hat im Bereich der Inertialsensorik die Poly-Silicon MEMS Technologieplattform PSM-X2 entwickelt, einen Prozess für die Polysilizium-Oberflächen-Mikromechanik. Die Kombination von Beschleunigungssensoren, Drehratensensoren und Magnetfeldsensoren auf Chipebene erlaubt eine hochintegrierte, präzise und kostengünstige Fertigung von IMUs.

Charakteristik des Prozesses mit der PSM-X2-Technologieplattform

- Die µmirror und Akustik Bauelemente basieren auf einem Mikromechanik Prozess mit einer Siliziumschicht ("EpiPoly" bis 100 µm Dicke) für die bewegten Massen

- Verkappung der Bauteile auf Waferebene (Kappenwafertechnologie) für den Betrieb der Bauteile unter Vakuum

- Hermetische Verkapselung mit sehr geringen Leckraten durch eutektische Metallbondsysteme

- Einstellbarer Arbeitsdruck in den Sensorkavitäten (1 bar .... 10-2 mbar) mittels Wafer Level Packaging unter Vakuum und integrierter Getterschicht in den Kappenwafern

- Chip bezogener Leckratentest durch Anwendung des “Neon Ultra-Feinlecktest“

- Umsetzung von unterschiedlichen Arbeitsdrücken in zwei benachbarten Kavitäten auf einem Chip in einem Prozessschritt (Dual cavity approach)

- 100% Testabdeckung durch speziell entwickelte Endteststrategie

- Prozess qualifiziert für automobile Anwendungen (AEC Q100)

- Nachgewiesene Druckstabilität in den verkapselten Systemen über > 10 Jahre

Weiteres zum Thema Drehratensensor | Gyroscope:

Fraunhofer-Institut für Siliziumtechnologie

Fraunhofer-Institut für Siliziumtechnologie