Erweiterte Zusammenarbeit: CEA-Leti und Fraunhofer fördern Speichertechnologien für EU-Chips-Act

Hin zu energiesparenden Chips für Digital-, Analog- und Hochfrequenztechnik

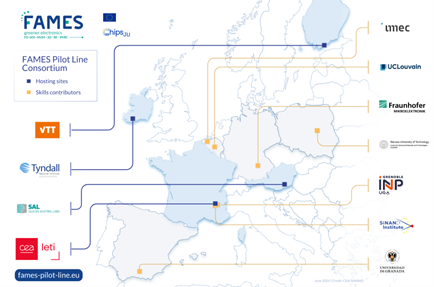

CEA-Leti und Fraunhofer planen eine Ausweitung ihrer Zusammenarbeit bei der Entwicklung und Integration neuartiger Speichertechnologien auf der Grundlage ferroelektrischer Materialien im Rahmen der kürzlich angekündigten FAMES-Pilotlinie (https://fames-pilot-line.eu/), einem Pionierprojekt zur Förderung der Halbleitertechnologien in Europa. Diese Initiative steht im Einklang mit den Zielen des EU-Chipgesetzes, das die Halbleiterkapazitäten der EU stärken und die technologische Souveränität gewährleisten soll.

Die Pilotlinie wird fünf neue Technologien entwickeln:

- FD-SOI (mit zwei neuen Generationsknoten bei 10nm und 7nm),

- verschiedene Arten von eingebetteten nichtflüchtigen Speichern (OxRAM, FeRAM, MRAM und FeFETs),

- Hochfrequenzkomponenten (Schalter, Filter und Kondensatoren),

- Zwei 3D-Integrationsoptionen (heterogene Integration und sequentielle Integration) und

- kleine Induktoren zur Entwicklung von DC-DC-Wandlern für integrierte Stromversorgungsschaltungen (Power Management Integrated Circuits, PMIC).

Die fünf neuen Technologien werden Marktchancen für stromsparende Mikrocontroller (MCU), Multiprozessoreinheiten (MPU), innovative KI- und maschinelle Lerngeräte, intelligente Datenfusionsprozessoren, RF-Geräte, Chips für 5G/6G, Chips für den Automobilmarkt, intelligente Sensoren und Bildgeber, vertrauenswürdige Chips und neue Raumfahrtkomponenten eröffnen. "Durch die Integration und Kombination einer Reihe von Spitzentechnologien wird die FAMES-Pilotlinie die Tür zu bahnbrechenden System-on-Chip-Architekturen öffnen und intelligentere, umweltfreundlichere und effizientere Lösungen für zukünftige Chips bieten. Das FAMES-Projekt wird in der Tat den Herausforderungen der Nachhaltigkeit von Halbleitern besondere Aufmerksamkeit widmen", sagte Jean-René Lèquepeys, CTO von CEA-Leti.

Die Pilotlinie wird allen EU-Akteuren (Universitäten, RTOs, KMUs und Industrieunternehmen) und allen gleichgesinnten Ländern im Rahmen jährlicher offener Aufforderungen und auf Anfrage nach einem fairen und nicht diskriminierenden Auswahlverfahren zugänglich sein. Das Projekt wird zu gleichen Teilen von den teilnehmenden Mitgliedstaaten und dem Chips JU finanziert. "Das Chips Joint Undertaking (Chips JU) ist stolz darauf, einen Beitrag zu dieser strategischen Initiative zu leisten und die Souveränität der EU in einem wichtigen Bereich zu stärken. Diese Pilotlinie wird wesentliche Halbleitertechnologien vorantreiben und dabei einen starken Fokus auf Nachhaltigkeit legen und die Zusammenarbeit zwischen mehreren europäischen Akteuren fördern. Das Gemeinsame Unternehmen Chips soll als Katalysator und Modell für weitere öffentliche und private Kooperationen in Schlüsselbereichen dienen", erklärte Jari Kinaret, der Exekutivdirektor des Gemeinsamen Unternehmens Chips.

Das FAMES-Konsortium vereint eine hervorragende Gruppe von Partnern:

- der Koordinator der Pilotlinie, CEA-Leti (Frankreich),

- imec (Belgien),

- Fraunhofer (Deutschland),

- Tyndall (Irland),

- VTT (Finnland),

- CEZAMAT WUT (Polen),

- UCLouvain (Belgien),

- Silicon Austria Labs (Österreich),

- SiNANO Institut (Frankreich),

- Grenoble INP-UGA (Frankreich),

- Universität von Granada (Spanien).

Im Rahmen des geplanten Fraunhofer-Beitrags zur Pilotlinie bringen drei Fraunhofer-Institute ihre Expertise ein:

Das Fraunhofer-Institut für Photonische Mikrosysteme IPMS mit seinem Center Nanoelectronic Technologies (CNT)

Im Center Nanoelectronic Technologies betreibt das Fraunhofer IPMS angewandte Forschung auf 300-mm-Wafern für Mikrochipproduzenten, Zulieferer, Gerätehersteller und F&E-Partner. Die Forschung umfasst Themen wie 300-mm-Frontend-Technologiemodule, Testchips, Energiespeicher und Speichertechnologie der nächsten Generation. In dieser Kooperation bringt das Fraunhofer IPMS seine einzigartige Erfahrung in den Bereichen Optimierung des ferroelektrischen HfO2-Materials, Stack-Benchmarking, Modulentwicklung und Bauteiloptimierung ein, während CEA-Leti eine einzigartige Pilotlinie einbringt, die die Integration von FeRAM oder FeMFET auf CMOS-Wafern bis hinunter zum 22-nm-Knoten ermöglicht, die für dichte und 300-mm-große Speicherarrays geeignet ist, die für energieeffiziente KI-Beschleuniger verwendet werden.

Fraunhofer-Institut für Siliziumtechnologie ISIT

Das Fraunhofer ISIT entwickelt in seinem 200-mm-Reinraum fortschrittliche Post-CMOS- und III-V-Bauelemente und -Systeme. Diese decken den Anwendungsbereich von MEMS über Mikro- bis hin zu Leistungselektronik ab. In der Vergangenheit wurden am Fraunhofer ISIT ferroelektrische AlScN-Dünnschichten entdeckt und BEOL-FeFETs erfolgreich prozessiert. Im Rahmen dieser Aktivitäten werden neuartige ferroelektrische Materialien auf Nitridbasis etabliert und für die Integration in CMOS-Speicher-Benchmark-Fahrzeugen evaluiert. Neben der Speicherstapelverarbeitung wird das ISIT auch die BEOL-CMOS-Verarbeitung abschließen. Das Ziel ist eine gründliche Evaluierung von FeRAM auf Nitridbasis, die eine extreme Haltbarkeit (>100 Jahre, >500°C) versprechen.

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM mit seinem All Silicon System Integration Center Dresden (ASSID)

Die Schwerpunkte des Fraunhofer IZM liegen in der Aufbau- und Verbindungstechnik und der Integration von multifunktionaler Elektronik in Systeme. Im Rahmen der Pilotlinie wird die Abteilung "Wafer Level System Integration" (WLSI) am ASSID fortschrittliche Packaging- und Systemintegrationstechnologien für neue Speichertechnologien auf 300 mm-Wafern in 2,5- und 3D-Stacks entwickeln und einsetzen. Darüber hinaus wird die Abteilung für Environmental & Reliability Engineering heutige und zukünftige Speichertechnologien und deren Integrationsansätze im Hinblick auf ihre Nachhaltigkeit bewerten. Unter Umwelt- und Nachhaltigkeitsgesichtspunkten bieten Systemlösungen auf der Basis ferroelektrischer Speicher Vorteile gegenüber modernen Lösungen, da die geringe Schaltleistung die Lebensdauer der Bauelemente erhöht und das Anwendungsportfolio von selbstversorgten Systemen erweitert. Darüber hinaus trägt die niedrige Schaltspannung im Vergleich zu konventionellen Floating-Gate-Speichern zu einer erheblichen Verringerung der Chipfläche und damit zur Reduzierung von Energie, Chemikalien und Rohstoffen bei der Chipherstellung bei. Diese Verbesserungen bei der Chipfläche und der Leistung werden im Rahmen der Zusammenarbeit überwacht und verglichen werden.

Ein europäisches Konsortium unter der Koordination der Forschungsfabrik Mikroelektronik Deutschland (FMD) beabsichtigt, in den nächsten Jahren die umfassendste und modernste Pilotlinie für "Advanced Heterogeneous System Integration" als Beitrag zur Umsetzung des EU-Chipgesetzes aufzubauen. Die Beteiligung von CEA-Leti und anderen europäischen Partnern an der oben genannten Pilotlinie wird ähnlich sein wie die Beteiligung der Fraunhofer-Institute IPMS, IZM und ISIT an der FAMES-Pilotlinie. Ziel dieser Bemühungen ist es, eine enge inhaltliche Verbindung zwischen den kommenden paneuropäischen Pilotlinien zu gewährleisten.

Fraunhofer-Institut für Siliziumtechnologie

Fraunhofer-Institut für Siliziumtechnologie