Katja Reiter

Anfertigung von Flächenschliffen zur Beurteilung von Verbindungsflächen bei elektronischen Aufbauten und Komponenten

Zur Qualitätsbeurteilung elektronischer Aufbauten und Komponenten werden hauptsächlich metallographische Querschliffe angefertigt, um Details im Mikrometerbereich verlässlich darstellen zu können. Diese Querschliffe zeigen jedoch von der eigentlichen Verbindung immer nur einen Teilbereich der Fügezone. Für die Analyse interessant sind z. B., Materialzusammensetzung, Gefügeaufbau, Verteilung von Phasenbestandteilen, sowie Inhomogenitäten wie Lunker, Hohlräume und Risse. Es ist jedoch schwierig, größere Flächen von Fügezonen mit Schichtdicken von wenigen Mikrometern planparallel zu präparieren.

Im ISIT ist eine neue Präparationstechnik zur Anfertigung von Flächenschliffen entwickelt worden.

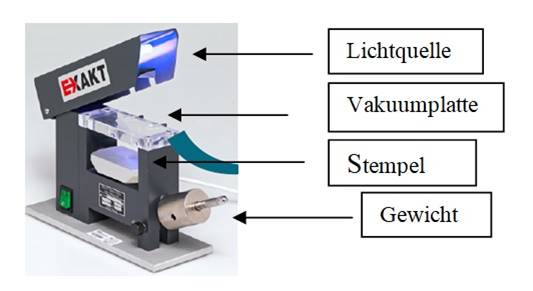

Die Versuche wurden an verschiedenen Komponenten aus der Elektronik auf einer Schleifmaschine, die ursprünglich für die Präparation von Dünnschliffen in der Histologie verwendet wird, durchgeführt (Bild links). Die größte Herausforderung bei der Erststellung von Flächenschliffen liegt in der exakten planparallelen Fixierung der Probe auf dem Probenhalter. Beim Anschleifen der Proben ist die Auswahl der Schleif und Poliermedien von besonderer Bedeutung, wenn man eine Artefakt freie Oberfläche mikroskopisch darstellen möchte. Mit Hilfe eines hochpräzisen Messsystems wurde die μ-genaue Einstellung und Vermessung des Schleifabtrages bei geringster mechanischer und thermischer Belastung der Probe ermöglicht.

Proben können auf einem Objektträger der Größe 50 mm x 100 mm mit einem UV aushärtenden Kleber in einer Einbettpresse mit UV-Licht befestigt werden (Bild rechts). Der Abtrag der Probe erfolgt durch Oszillation mittels gravimetrisch eingestellter Schleifkraft. Toleranzen von wenigen Mikrometern werden durch einen stabilen und erschütterungsfreien Lauf des Schleiftellers garantiert.

Der Probenabtrag wird mittels eines LVDT-Sensors (Wege von 10 Millimeter mit einer Auflösung von 1 Mikrometer) gemessen. Der Anpressdruck wird mit Hilfe von Gewichten von 100 g oder 200 g eingestellt.

Präparationsbeispiele

1 Silber- Sinterschicht

Das Silbersintern gewinnt immer mehr an Bedeutung in der Leistungselektronik, z.B. bei der Herstellung von Wechsel- oder Gleichrichtern in den verschiedensten Anwendungsbereichen von Bahntechnik bis hin zur Windkrafttechnik. Bei Leistungsmodulen werden DCB-Substrate (Direct Copper Bonded) mit Dioden, IGBTs (Insulated-Gate Bipolar Transistor) oder Power MOSFETs (Metall Oxide Semiconductor Field Emitting Transistor) bestückt, welche in ein Gehäuse verbaut werden.

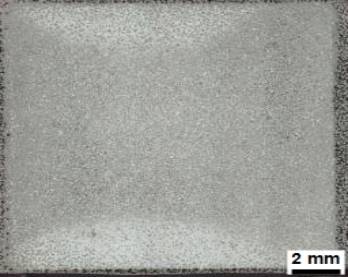

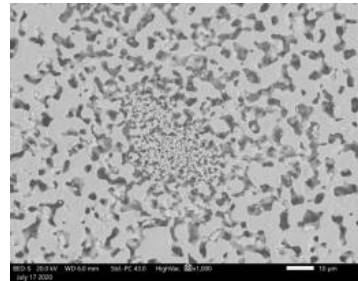

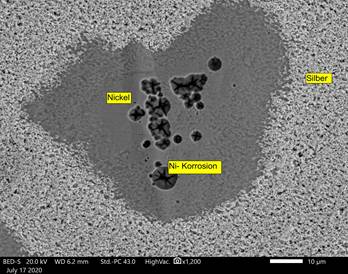

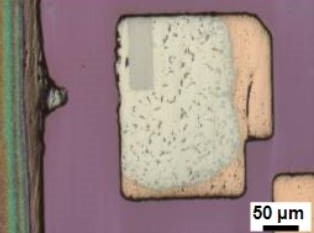

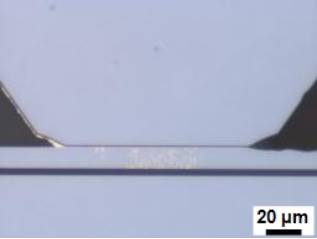

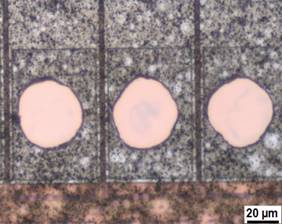

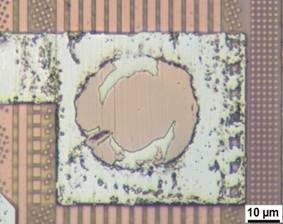

Zur Beurteilung von Sinterschichten ist für die Qualität der Verbindungsschicht die Porosität ein Maß für die Güte der Verbindung. Die Porosität in einer Sinterschicht kann bis zu 30% betragen. Sie ist abhängig vom Herstellungsverfahren und von der verwendeten Silberpaste. In den unteren Bildern werden verschiedene Ebenen einer 20µm dünnen Silber –Sinterschicht, die ein Siliziumsubstrat mit einem DCB –Substrat verbindet, dargestellt. Hierfür wurde der Siliziumchip abgeschliffen, die Silberschicht poliert und anschließend mit einem Ionenstrahl bearbeitet, um die Poren freizulegen.

2 Bondrahmen von MEMS-Bauelementen (Micro-Electro-Mechanical System)

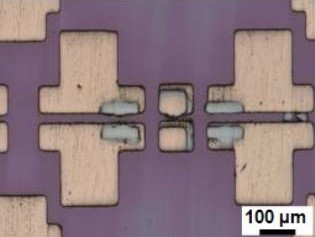

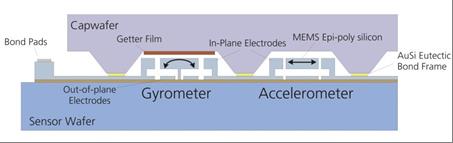

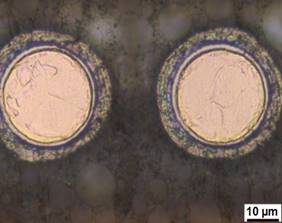

Zur Fertigung und Verkapselung von MEMS- Bauelementen werden Silizium- bzw. Glaswafer durch eine Metallisierung aus z.B. Kupfer-Zinn, Gold-Zinn bzw. Gold-Silizium miteinander verbunden. Bei der Verkapselung müssen die Verbindungen (Bondrahmen) z.T. hermetisch dicht sein und dürfen keine Poren aufweisen, um den Anforderungen zu genügen. Die Füge-Schichtdicken betragen oft nur wenige Mikrometer.

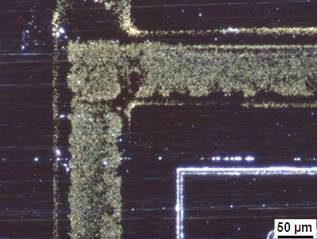

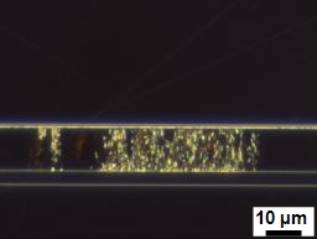

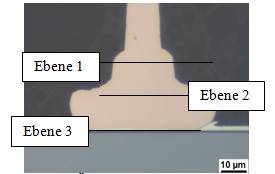

In den drei unteren Bildern wird eine Verbindung aus Kupfer und Zinn im Flächenschliff dargestellt. Der Fügebereich beträgt 10µm.

Das obere Bild zeigt die Fügezone im Querschliff. Zu erkennen sind oben und unten reines Kupfer und in der Mitte der Fügezone die intermetallischen Phasen Cu3Sn (dunkelgrau) und Cu6Sn5 (hellgrau).

3 Bondrahmen aus einer Gold Metallisierung

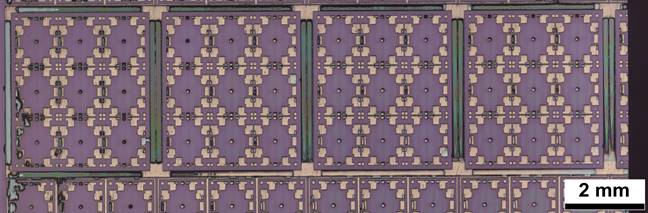

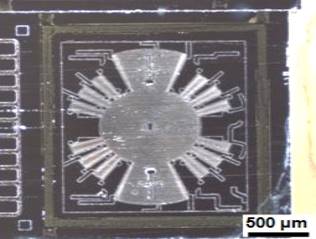

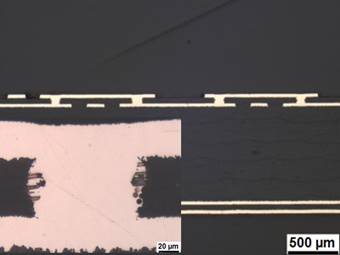

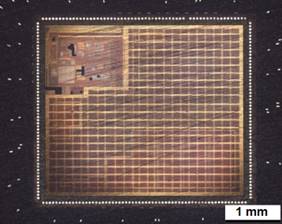

An einem Drehratensensor (Bild mitte) wird der 10µm dicke Bondrahmen aus Gold-Silizium präpariert.

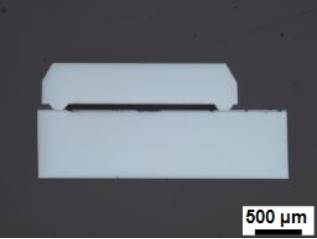

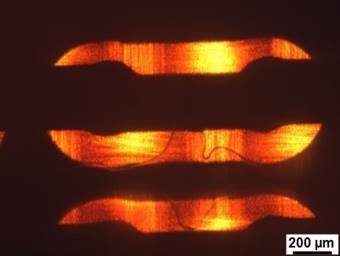

Die unteren Bilder zeigen Übersichts- und Detailaufnahmen dieses AuSi-Bondrahmens im Querschliff. Eine zusätzliche Herausforderung bei dieser Präparation ist, dass das MEMS Bauelement aus mehreren Ebenen von 10µm dünnen Siliziummembranen besteht. Die beiden oberen Bilder rechts und links zeigen die Verbindungszone mit Membran im Flächenschliff.

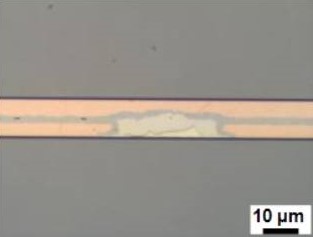

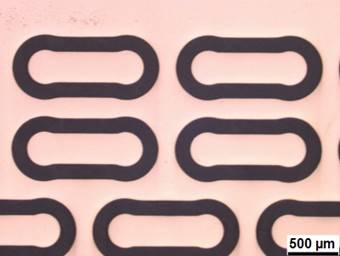

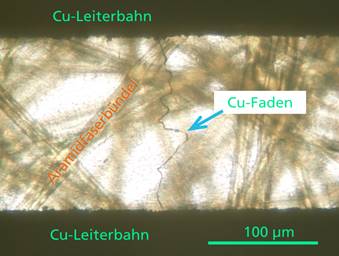

4 Leiterplattenqualität

Schädigungen in den Kupferleiterbahnen können zum Ausfall eines elektronischen Gerätes führen. Das Bild oben links zeigt einen Leiterplattenausschnitt mit µ-Vias. Zur Beurteilung der Leiterplattenqualität kann ein Flächenschliff zum Beispiel den Aufbau der Kupferleiterbahnen und Durchkontaktierungen (Bilder oben mittig & rechts, sowie unten links) oder Kupferfäden zwischen zwei Leiterbahnen (unten rechts) darstellen.

5 Beurteilung von Drahtbondverbindungen

Bei einem Ball Grid Array (BGA) wurde das Kunststoffgehäuse bis auf die Chipebene soweit abgeschliffen, dass man alle Bonddrähte auf gleicher Höhe erkennen kann (unten links). In weiteren Ebenen wurden die verschiedenen Bondbereiche anpoliert, so dass man den Drahtbond bzgl. der Korngröße und die Anbindungsfläche hinsichtlich der Phasenausbreitung beurteilen kann (obere Bilder & Bild unten rechts).

Fazit

Flächenschliffe sind eine sinnvolle Ergänzung der herkömmlichen metallographischen Querschliffpräparation. Diese wird im ISIT in Forschungsprojekten und für Industriekunden bei der Qualifizierung und Schadensanalyse von elektronischen Bauelementen und Baugruppen erfolgreich angewendet.

Das könnte Sie auch noch interessieren

Fraunhofer-Institut für Siliziumtechnologie

Fraunhofer-Institut für Siliziumtechnologie