Jenik Grimsmann

Taktzeitverkürzung im SMD-Fertigungsprozess am Beispiel einer Kundenbaugruppe durch Optimierung eines Konvektions-Lötprozesses unter Qualitätswahrung.

Am Fraunhofer ISIT wurde in der Arbeitsgruppe Modul-Services des Geschäftsfeldes Mikro-Fertigungsverfahren im Rahmen einer Abschlussarbeit zur Ausbildung eines Mikrotechnologen die Taktzeitverkürzung an einem Konvektionslötofen unter Qualitätswahrung realisiert.

Ausgangspunkt war ein bestehendes Lötprofil. Dieses sollte so optimiert werden, dass eine Durchsatzerhöhung erreicht wird, ohne dass dies zu qualitativen Einbußen am fertigten Produkt führt.

Dazu wurde zunächst mittels einer Simulationssoftware ein Vorschlag für eine Ofeneinstellung erarbeitet, indem die Transport-Geschwindigkeit und die Temperatur der einzelnen Heizzonen als Parameter variiert wurden.

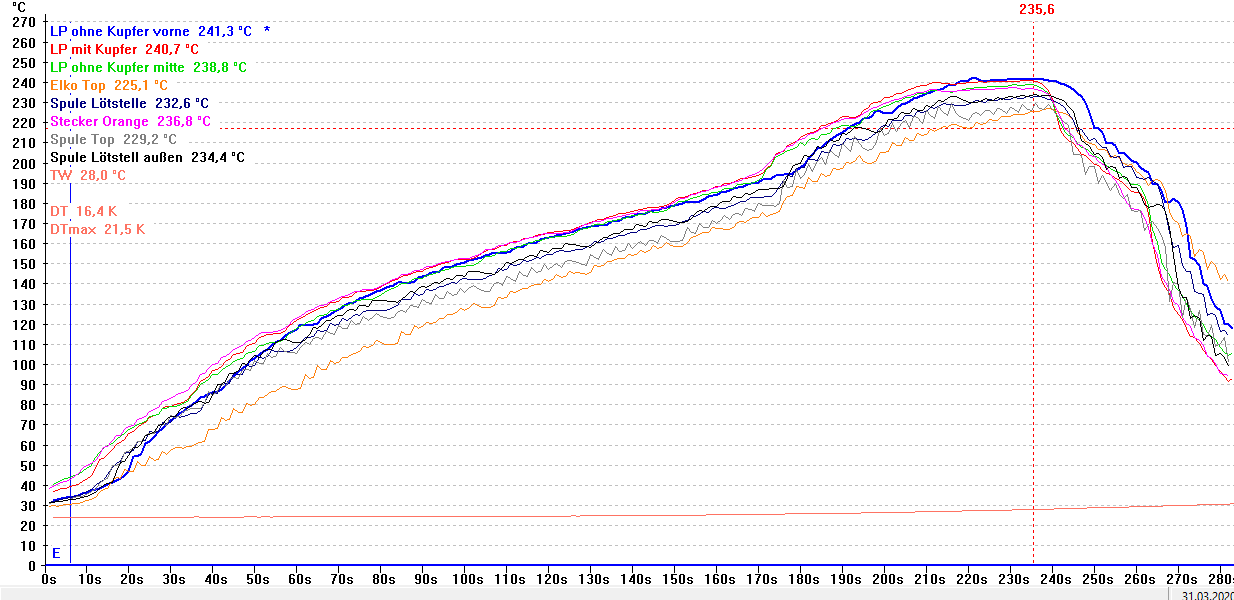

In Anschluss daran wurden Temperaturmessungen an einer Musterbaugruppe durchgeführt. Dazu wurden Mantelthermoelemente vom Typ K an Lötstellen und an thermisch sensitiven Komponenten angebracht. Das Ziel im Lötprozess bestand darin an den Lötstellen ausreichend Wärme für eine stoffschlüssige Lötverbindung bereitzustellen, ohne wärmeempfindliche Komponenten oder die Leiterplatte zu überlasten. Das Ergebnis der Messungen waren drei potentielle Parametersätze für die Ofeneinstellung. Das Muster einer Temperaturmesskurve ist in Abb. 1 dargestellt.

Die Analyse der Temperaturmessungen ergab, dass mit zunehmender Transportgeschwindigkeit sowohl die Lötstellentemperaturen als auch die Zeiten über Liquidus (Lot in der schmelzflüssigen Phase) sanken.

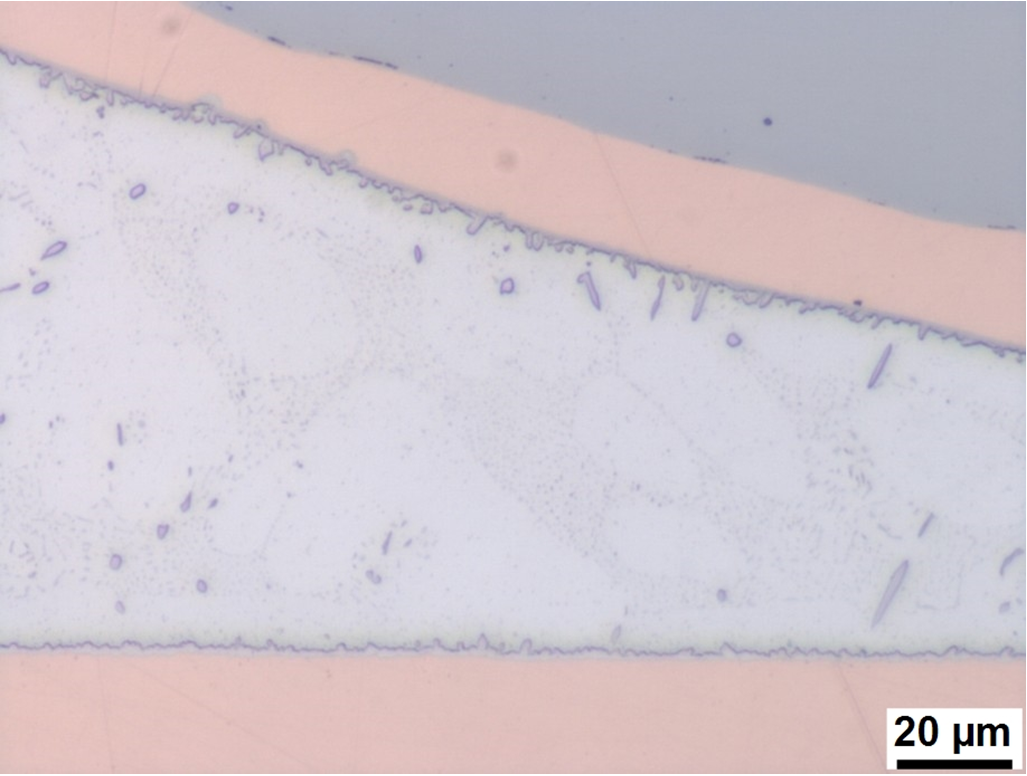

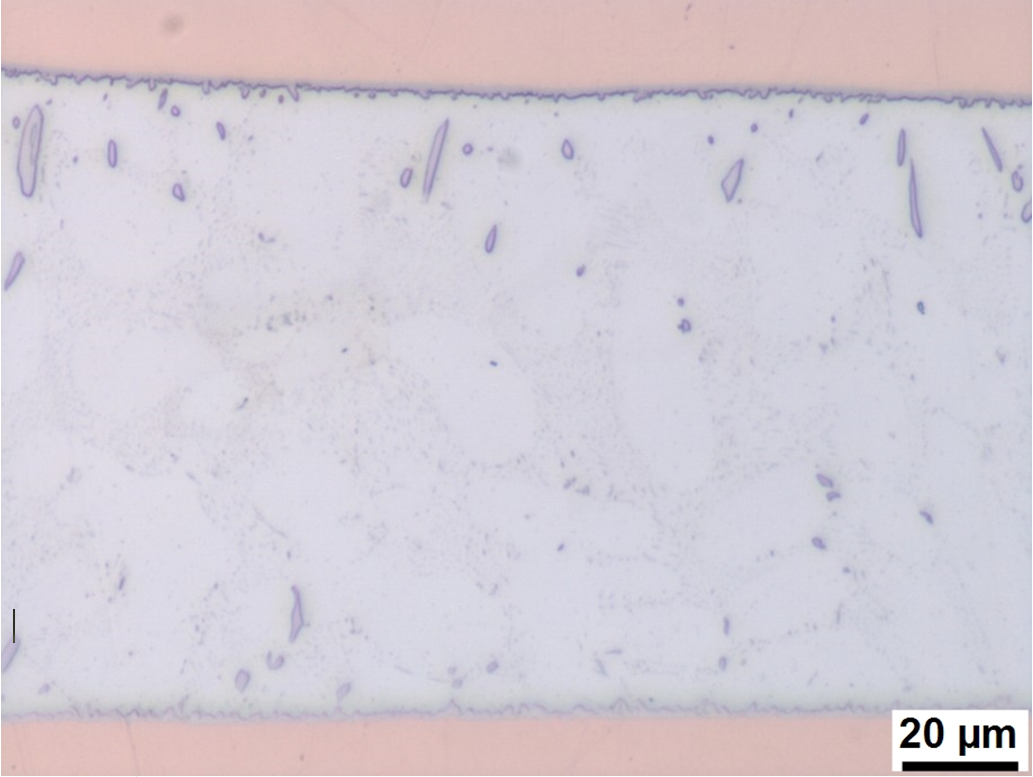

Mit den erarbeiteten Parametersätzen wurden Testmuster aufgebaut und eine Qualitätsprüfung an den Baugruppenmustern durchgeführt. Sowohl optisch als auch mittels Röntgenprüfung waren keine signifikanten Unterschiede zwischen den verschiedenen Lötprofilen zu erkennen. Alle Baugruppen wiesen keine Lötfehler, Beschädigungen oder Auffälligkeiten auf. Es folgte eine Querschliffanalyse, um sowohl die Lötstellenqualität als auch die strukturelle Integrität der Baugruppe zu beurteilen. Schäden an Komponenten oder Leiterplatte konnten auch im Querschliff nicht festgestellt werden. Alle Lötstellen wiesen eine gute Benetzung und eine durchgehende intermetallische Phasenschicht auf. Lediglich bei dem Lötprofil mit der höchsten Transportgeschwindigkeit war eine leicht verringerte intermetallische Zone zu erkennen, siehe Abb. 2 - 3.

Im Fertigungsprozess elektronischer Baugruppen kann es immer wieder zu Schwankungen in der Anlieferqualität beigestellter Materialien kommen. So kann zum Beispiel die Dicke der angelieferten Leiterplatten um +/- 10% schwanken und sich dennoch im zulässigen Prozessfenster befinden. Diese Toleranz hat aber einen entscheidenden Einfluss auf die Wärmekapazität der Baugruppe. Grenzwertig kalte Lötprofile könnten im Falle einer dickeren Leiterplatte (höherer Lötwärmebedarf) zu Nichtlötungen führen.

Um den Lötprozess stabiler und trotz erhöhtem Durchsatzes weniger anfällig zu gestalten, sprich das Prozessfenster des Lötprozesses auf zu weiten, wurde nicht die getestete maximale Transportgeschwindigkeit für die Parameteroptimierung gewählt, sondern eine etwas langsamere Geschwindigkeit. So wurde bei Qualitätswahrung eine deutliche Erhöhung des Durchsatzes erreicht, womit das Ziel der Projektarbeit erreicht wurde.

Das ISIT bietet Technologieberatung und Unterstützung bei der Prozessevaluierung und Optimierung an. Gerne stehen wir Ihnen für individuelle Fragestellungen zur Verfügung.

Fraunhofer-Institut für Siliziumtechnologie

Fraunhofer-Institut für Siliziumtechnologie