Mario Reiter

Entwicklung, Fertigung und Bereitstellung von Testwafern mit Strukturen in Glas oder Silizium

Materialscreening, Prozessentwicklung und Maschinenqualifizierung sind typische Szenarien für den Einsatz von Testwafern. Während Produktwafer meist teuer und schwer zu beschaffen sind, lassen sich Testwafer kostengünstig produzieren und auf die jeweiligen Anforderungen maßschneidern. Neben standardisierten Komponenten für typische Anwendungen bietet das ISIT auch kundenspezifischen Lösungen an.

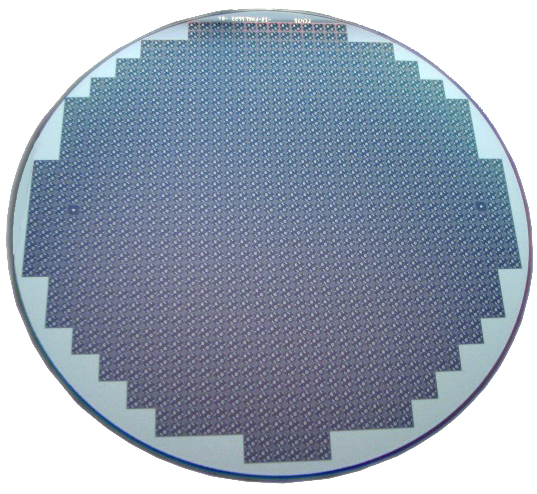

Zur Verfügung stehen verschiedene Trägermaterialien (Glaswafer, Siliziumwafer). Die Wafer werden im 8 Zoll-Format gefertigt, d.h. die Wafer sind rund und haben einen Durchmesser von 200mm.

Es stehen 2 Oberflächen (Ober- / Unterseite des Wafers) zur Behandlung zur Verfügung. Die Wafer können mit verschiedenen metallischen Oberflächen (z.B. Al, Cu, Ni, Au, Ag) beschichtet werden.

Für unterschiedliche Schichtdickenbereiche (nm- Bereich bis µm- Bereich) stehen entsprechend unterschiedliche Metallabscheidungsvarianten (z.B. Aufdampfen, Sputtern, galvanische Metallabscheidung zur Verfügung. Um die Haftfestigkeiten der Metalle auf den Wafern zu garantieren, werden Haftvermittlerschichten verwendet. Als Haftvermittlerschichten kommen verschiedene Plating-Base-Systeme (wie z.B. WTi, TiPtAu, CrAu) zum Einsatz.

Neben der Metallabscheidung können auch Isolatorschichten (z.B. Si3N4, SiO2) erzeugt werden.

Durch Verwendung von entsprechend strukturierten Belichtungsmasken können die Wafer fast beliebig bis in den Submikrometer-Bereich strukturiert werden. Dabei werden die Wafer je nach Genauigkeitsanforderungen komplett oder in Teilschritten (mit sogenannten Steppern) belichtet. Hierbei sind mehrere Belichtungs-, bzw. Prozessebenen auf einem Wafer möglich. Bei der Erstellung des Masken-Layouts verwenden die ISIT-Mitarbeiter, die langjährige Erfahrung im Maskendesign haben, gängige Design-Tools. Anschließend erfolgt die Beschaffung der physischen Masken.

Die 8 Zoll-Wafer aus Silizium oder Glas haben eine Standard-Dicke von 725µm. Glaswafer können auch mit geringerer Dicke (z.B. 400µm) bereitgestellt werden. Bei Bedarf können die Wafer durch einen nachfolgenden Grinding-Prozess gedünnt werden (Siliziumwafer auf etwa 100µm, Glaswafer auf etwa 200µm).

Auf einen 8 Zoll-Wafer passen je nach Anwendung (Größe) bis zu einige 100 Einzelchips. Um diese zu vereinzeln, wird der Wafer auf eine Folie laminiert und in die entsprechenden Einzelchips gesägt. Typische Schnittbreiten für Silizium-Wafer sind 35µm. Es ist auch möglich, Grinding- und Sägeprozesse als Dienstleistung anzubieten, d.h. der Kunde stellt selbst die zu bearbeitenden 8 Zoll-Wafer zur Verfügung.

Für die Testwafer sind vielfältige Anwendungen denkbar, im Folgenden werden einige Beispiele und Anregungen gegeben.

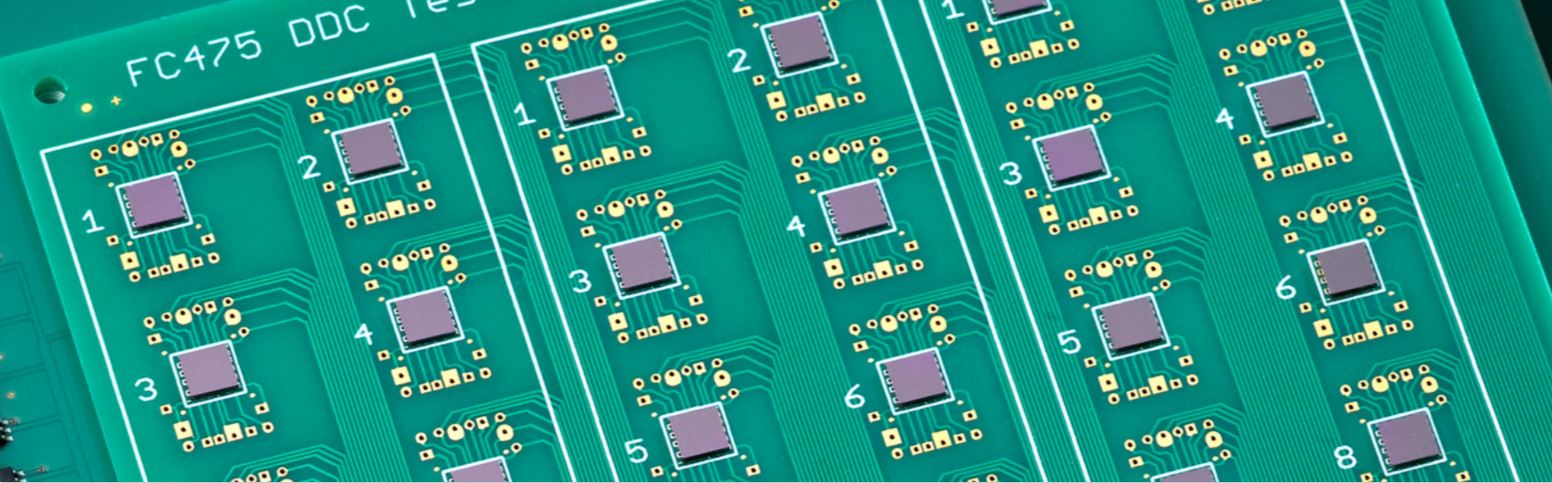

Zur Beurteilung von elektrischen Verbindungen (Löten, Kleben, Sintern) hinsichtlich Herstellqualität und Zuverlässigkeit eignen sich beispielsweise Siliziumchips, deren Kontakte paarweise verbunden sind (Daisy-Chain-Strukturen). Werden diese auf das dazugehörige Substrat (z.B. eine Leiterplatte) bestückt, lässt sich leicht prüfen ob alle Kontakte verbunden sind und ob Kurzschlüsse vorliegen.

Mit diesen schon zur Verfügung stehenden Testchips lassen sich z.B. Löt- oder Klebverbindungen charakterisieren. Durch entsprechende Kontaktwiderstandsmessungen während oder nach Alterungsbelastungen lassen sich auch Aussagen zur Zuverlässigkeit der erzeugten Verbindungen generieren. Eine weitere Anwendung sind z.B. rückseitenmetallisierte Testchips mit einer Silberbeschichtung, die z.B. für Sinterversuche bereitstehen, um den Sinterprozess bei Leistungshalbleitern zu optimieren (Verwendung unterschiedlicher Sinterpasten und Verarbeitungsparameter).

Mit Hilfe von Testchips lassen sich aber auch Oberflächenwiderstände mittels Kammstrukturen auf und unter Bauteilen messen.

Man kann so Erkenntnisse über die Verhältnisse unter Bauteilen bei Klimalast gewinnen. Typische Anwendungen wären die Evaluierung von Verunreinigungen z.B. durch Löt-Flussmittel, die Bestimmung der Güte von Reinigungsprozessen oder der Nachweis der Wirksamkeit von Lackierungen.

Glaswafer werden hingegen oft für optische Anwendungen verwendet.

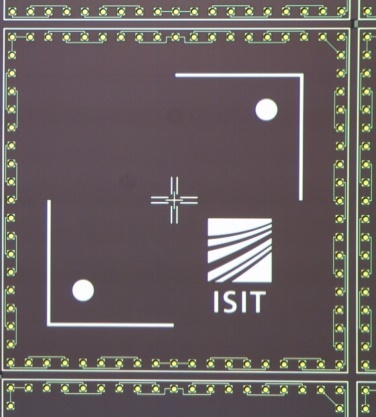

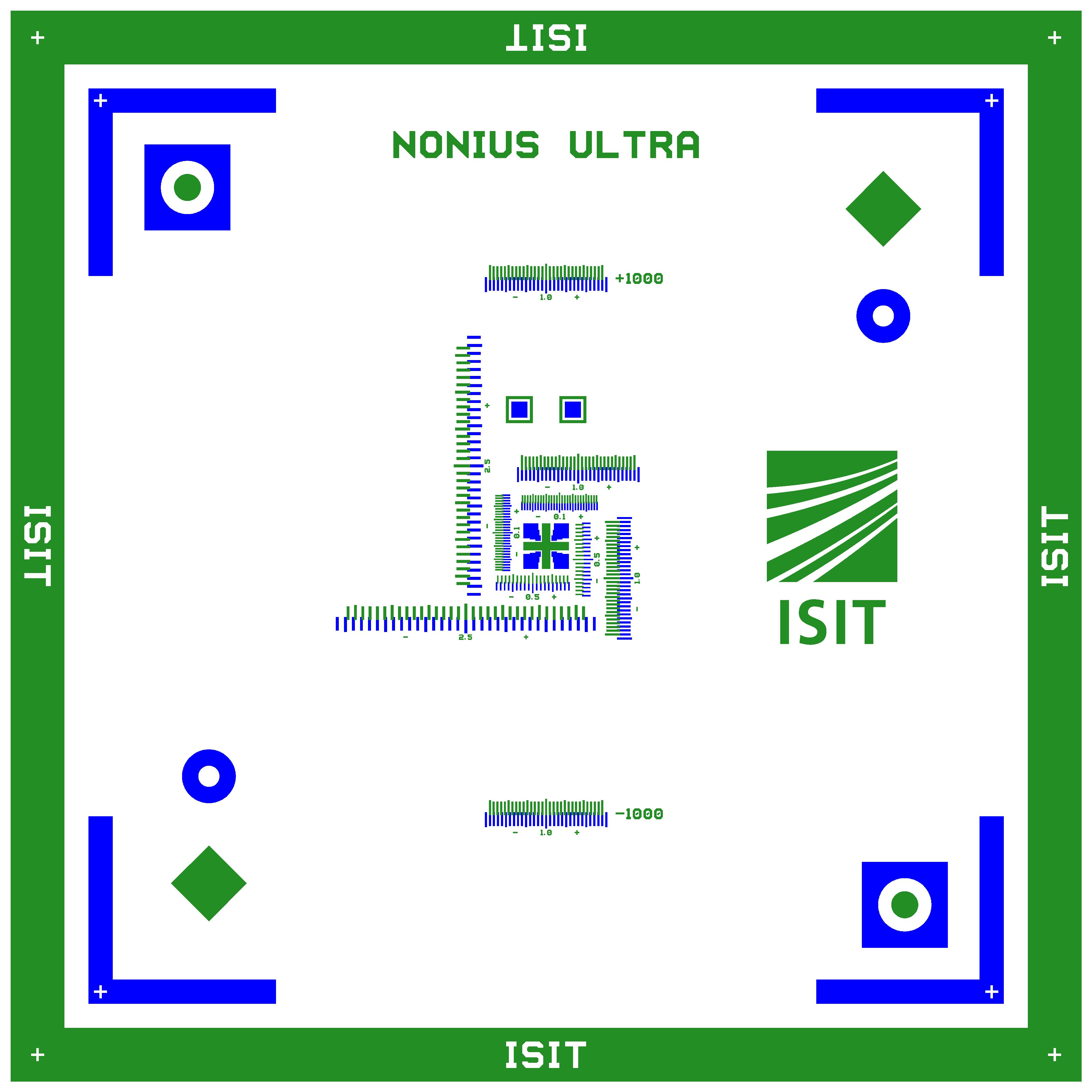

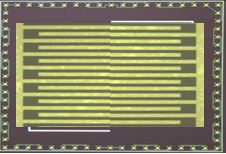

Zum Nachweis der Positioniergenauigkeit von Maschinen bei der Kundenabnahme oder auf Messen eignen sich Nonius-Strukturen auf Glaschips.

Die optischen Strukturen werden in einen Substratchip (blau) und einen Deckchip (grün) eingebracht. Mithilfe der Markierungen (Aluminium-Pads) auf den beiden Chips lässt sich die Platziergenauigkeit (Verschiebung, Rotation) z.B. von Pick & Place-Maschinen vermessen.

Testwafer bieten vielseitige Möglichkeiten – hier wurden nur einige wenige Beispiele genannt. Sprechen Sie uns gerne an, wenn Sie Interesse an schon vorhandenen Lösungen haben. Bestimmt haben Sie eigene Ideen und Wünsche. Gerne können wir gemeinsam mit Ihnen neue, herausfordernde und interessante Anwendungen entwickeln.

Das könnte Sie auch noch interessieren

Fraunhofer-Institut für Siliziumtechnologie

Fraunhofer-Institut für Siliziumtechnologie