Tim Alexander Barnbrock

Sichere Strommessung in SIR-Tests bei hohen Spannungen

Zur Qualifikation von Materialien, die in der Elektronikfertigung zum Einsatz kommen, wie z.B. Flussmittel und Lötstopplacke werden am ISIT unter anderem Messungen des Oberflächenisolationswiderstandes durchgeführt. Hierzu wird auf Teststrukturen z.B. Flussmittel oder Lotpaste aufgetragen, einer Lötwärmebelastung unterzogen und anschließend unter angelegter Gleichspannung in einem Prüfklima ausgelagert.

Die zunehmende Verbreitung von Hochspannungsanwendungen in der Leistungselektronik und im Automotivbereich erfordert die Durchführung solcher SIR-Test Messungen (SIR = Surface-Insulation-Resistance) unter hohen Spannungen. Die Entwicklung eines Messstandes für bis zu 1.500 V anliegender Spannung wurde im Rahmen einer Bachelorthesis umgesetzt.

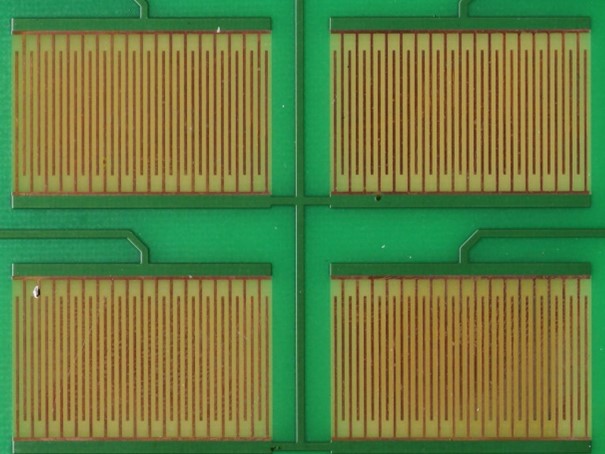

Bei SIR-Tests werden die Testobjekte klimatischem Stress ausgesetzt, um einen Betrieb der elektronischen Baugruppen in anspruchsvoller Umgebung über einen längeren Zeitraum zu simulieren. Bedingt durch die dabei vorherrschenden Temperaturen und die hohe Luftfeuchtigkeit treten beschleunigt Alterungserscheinungen auf. So lässt sich der Testzeitraum gegenüber dem Betrieb unter realen Bedingungen deutlich verkürzen, typischerweise auf ein bis mehrere Wochen. Während dieser Klimaauslagerung können durch ECM (elektrochemische Migration) elektrisch leitfähige Strukturen wachsen, sogenannte Dendriten. Dadurch nimmt der Oberflächenisolationswiderstand kontinuierlich ab und kann bei Überbrückung von Leiterzügen unterschiedlichen Potentials letztendlich zu Kurzschlüssen führen. Um diese Entwicklung zu prüfen; können Teststrukturen in ein funktionelles Layout integriert sein oder wie in Abbildung 1 aus einer freiliegenden Kammstruktur bestehen, deren Kämme sich nicht berühren. Zwischen ihnen befindet sich kein Lötstopplack, wodurch eine Verringerung des Oberflächenisolationswiderstandes dort am ehesten zu erwarten ist.

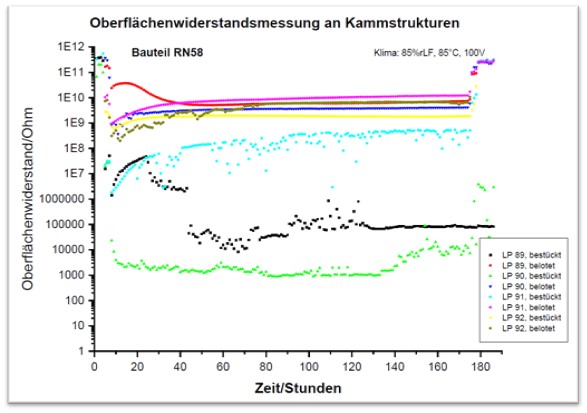

In Abbildung 2 ist ein typischer Verlauf der Messwerte während eines einwöchigen SIR-Tests zu sehen. Die klimatischen Bedingungen entsprachen dabei den Standard-Parametern von 85° C und 85% relativer Luftfeuchtigkeit. Bei den untersuchten Bauteilen handelt es sich um Widerstandsarrays des Typs RN58. Freiliegende Kammstrukturen als auch Kammstrukturen unter RN58 wurden untersucht.

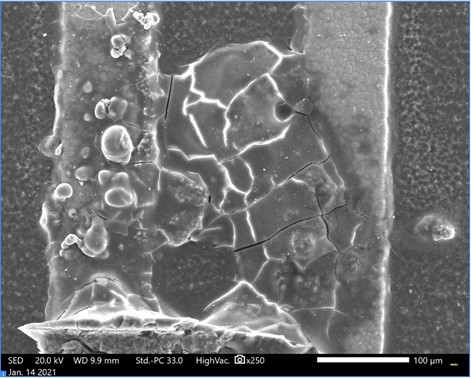

Die rasterelektronenmikroskopische Aufnahme aus Abbildung 3 stellt mit 250-facher Vergrößerung die Umgebung eines der Bauteile dar, welche im grünen Graphen aus Abbildung 2 repräsentiert werden. Der zulässige Grenzwert von 100 MOhm (1E8 Ohm) wurde deutlich unterschritten, was durch die gewachsenen Dendriten zu erklären ist. Der Widerstand ist nicht auf nahezu null abgefallen, da sich in der Messschaltung Schutzwiderstände zur Strombegrenzung befinden.

Ein weiteres Verfahren zur Qualifikation sind H3TRB (High-Temperature-High-Humidity-Reverse-Bias) Tests. Diese finden unter vergleichbaren klimatischen Bedingungen statt, dienen aber speziell der Qualifizierung von Halbleiter-Transistoren.

Dabei wird zwischen den Drain- und Source-Anschlüssen eine Spannung angelegt. Die ebenfalls vorhandene Basisspannung liegt unterhalb der Schwellenspannung des Transistors, der damit im Ausgangszustand des Tests nicht leitet. Durch die hohen klimatischen Belastungen kann es zu einer Beeinträchtigung der Eigenschaften des Halbleiters kommen. Ein Durchbruch der Basisspannung kann die Folge sein. Anders als bei SIR-Tests wird bei dieser Methode der Leckstrom, statt dem Widerstand aufgezeichnet und bewertet.

Im Rahmen der Bachelorthesis wurde ein 80-Kanal Messsystem entwickelt, bei dem jedem Kanal eine unterschiedliche Spannung zugewiesen werden kann. Dieses ist für beide Testverfahren geeignet. Somit können in Zukunft Materialien und Halbleiter-Bauteile aus dem Hochspannungsbereich am ISIT getestet werden.

Fraunhofer-Institut für Siliziumtechnologie

Fraunhofer-Institut für Siliziumtechnologie