The following elements of "classical" back-end technology are available as ISIT service offers:

- Mechanical dicing

- Wafer thinning (grinding and polishing)

- Aluminum and gold wire bonding

- Die attach (manual and fully automatic)

- Module integration: Chip-on-Board (COB), multichip module (MCM)

- Dispensing of encapsulants (glob top, dam-and-fill)

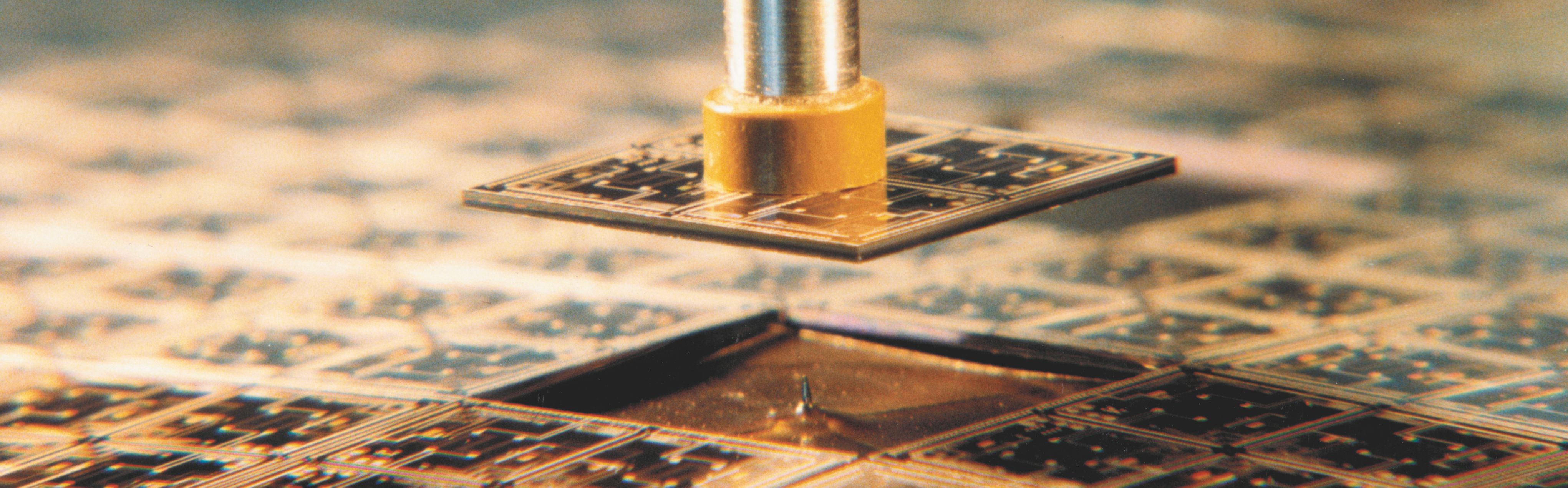

In extension of the back-end technologies based on wire bonding, the flip chip and chip-size packaging (CSP) are of great importance, especially for mobile applications. The Fraunhofer ISIT disposes of equipment and technology for all basic assembly methods:

- Flip chip bonding based on soldering, epoxy dip and stud bumping (ultrasound-assisted)

- Conditioning of wafers for flip chip or chip size packaging by solder balling and solder paste printing

- Dispensing of underfill adhesives

The Fraunhofer Institute for Silicon Technology offers an exhaustive selection of test chips and substrates for process and machine evaluation.

Fraunhofer Institute for Silicon Technology

Fraunhofer Institute for Silicon Technology